### An Extended Model for a Punch Through (PT)

### **Insulated Gate Bipolar Transistor (IGBT)**

#### **And Its Transient Characteristics**

#### A Thesis

Submitted to Department of Electrical and Electronic Engineering

of

#### **BRAC** University

By

Omar Saif; ID: 13121051 Md. Fazle Rabbi Pavel; ID: 13121069

Md. Akib Hasan; ID: 13121100 Asif Shah; ID: 14221027

Supervisor: Avijit Das, Lecturer, Department of EEE, BRAC University

In partial fulfillment of the requirements for the degree of Bachelor of Science in Electrical and Electronic Engineering

**BRAC** University

**Summer 2017**

## **Declaration of Authorship**

This is to declare that this thesis named "An Extended Model For A Punch Through (PT) Insulated Gate Bipolar Transistor (IGBT) And Its Transient Characteristics" is submitted by the authors listed for the degree of Bachelor of Science in Electrical and Electronics Engineering to the Department of Electrical of Electronics Engineering under the School of Engineering and Computer Science, BRAC University. We hereby affirm that the research work and result was conducted solely by us and no other. Materials of the study and work found by other researchers have been properly referred and acknowledged. This thesis paper, neither in whole nor in part, has been previously submitted elsewhere for appraisal.

Submission Date: 20th August, 2017

Avijit Das

Thesis Supervisor

Omar Saif

Md.Akib Hasan

Md. Fazle Rabbi Pavel

Asif Shah

## **Abstract**

The IGBT (Insulated gate bipolar transistor) is driven by MOSFET and has been modeled as a wide-base bipolar junction transistor (BJT). In our thesis we are proposing to make a new physical-base model for a punch though (PT) IGBT. By manipulating the different region length, depth and doping we will try to obtain better threshold and I-V relation regarding IGBT characteristics and make a new extended model with proper research on its transient characteristics.

## Acknowledgement

This note is made to express our gratefulness to some people who really encouraged and supported us a lot in making this report.

First of all, our sincere most thanks go to Avijit Das, Lecturer, Department of Electrical and Electronic Engineering, BRAC University, our respected supervisor of thesis who provided the idea about this topic. He has provided us with necessary materials & instructions which helped us a lot to understand the topic & analyze it better. He has always been there for us to rescue in case of any problems that we might encounter while dealing with this issue. Without his keen supervision, it was virtually impossible for us to finish this report successfully in time.

Finally, we are very grateful to the Almighty Allah, who has blessed us with knowledge and ability to write this report successfully.

## **Contents**

| Declaration of Authorship | i    |

|---------------------------|------|

| Abstract                  | ii   |

| Acknowledgement           | iii  |

| List of Figures           | vii  |

| List of Tables            | ix   |

| Abbreviation              | xi   |

| Physical Contents         | xii  |

| Symbols                   | xiii |

| 1 | Intr | troduction 1 |                                                          |        |

|---|------|--------------|----------------------------------------------------------|--------|

|   |      | 1.1<br>1.2   | Device Evaluation: BJT, MOSFET and IGBT                  | 3<br>5 |

| 2 | Bas  | ic Prin      | ciples of IGBT 7                                         |        |

|   | 2.1  | Basic        | Structure of IGBT                                        | 7      |

|   |      | 2.1.1        | Cross Sectional Structure of IGBT                        | 7      |

|   |      | 2.1.2        | NPT IGBT & PT IGB                                        | 8      |

|   |      | 2.1.3        | Difference Between NPT and PT IGBT                       | 10     |

|   | 2.2  | Switc        | hing Behavior of IGBT                                    | 11     |

|   | 2.3  | Princi       | iples of Operation of IGBT                               | 11     |

|   |      | 2.3.1        | Circuit Diagram of IGBT                                  | 11     |

|   |      | 2.3.2        | Equivalent Circuit of IGBT                               | 12     |

|   |      | 2.3.3        | IGBT Operation                                           | 14     |

|   | 2.4  | Basic        | Tools for operation                                      | 15     |

|   |      | 2.4.1        | The Steady state operation                               | 16     |

|   |      | 2.4.2        | The Transient State Operation                            | 19     |

|   | 2.5  | IGBT         | Generation Improvement                                   | 21     |

|   |      | 2.5.1        | Surface Structure                                        | 22     |

|   |      | 2.5.2        | Vertical Structure                                       | 26     |

| 3 | Lite | erature      | e review analysis 28                                     |        |

|   | 3.1  | Equat        | tions overview                                           | 28     |

|   |      | 3.1.1        | Poisson's Equation                                       | 28     |

|   |      | 3.1.2        | Carrier Continuity Equation                              | 28     |

|   | 3.2  | Allen        | R. Hefner Model                                          | 29     |

|   |      | 3.2.1        | Expression for Transient Voltage and Stored Charge Decay | 29     |

|   |      | 3.2.2        | Redistribution Time and Charge Control Current           | 35     |

| 4 | Sim  | ulatio       | ns 39                                                    |        |

|   | 4.1  | Atlas        | A Physically Based Simulator                             | 39     |

|   | 4.2  | Punch        | Through IGBT with Trench gate device structure           | 42     |

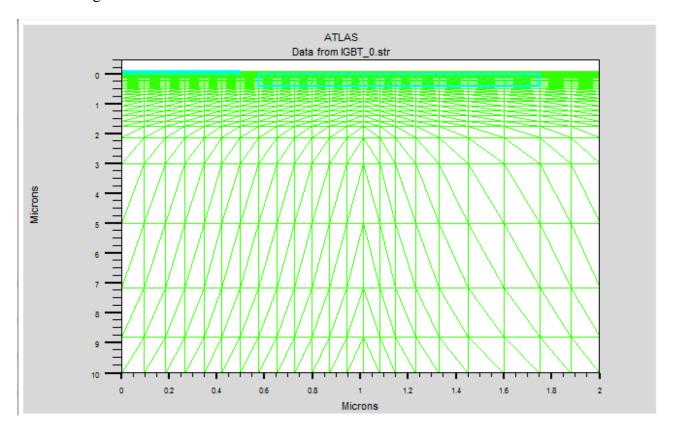

|   |      | 4.2.1        | Mesh Structure of the Trench IGBT                        | 42     |

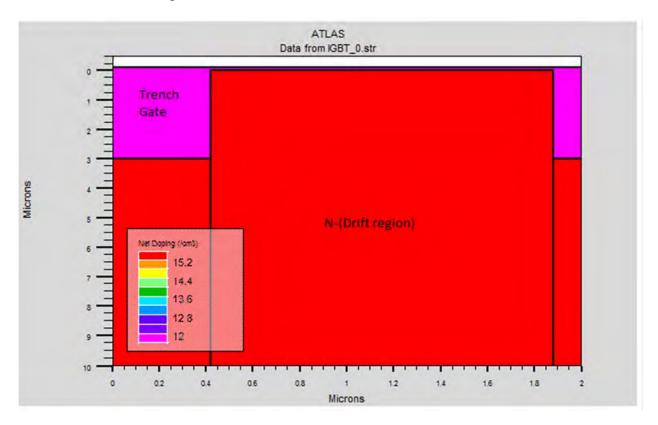

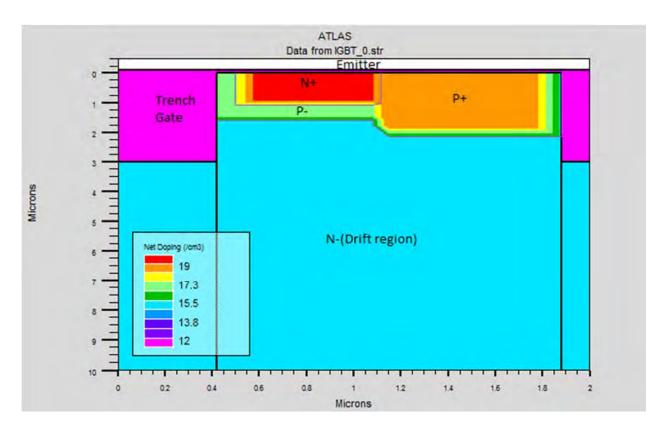

|   |      | 4.2.2        | Region and Doping formation                              | 43     |

|   | 4.2.3      | Device simulation                        | 45 |

|---|------------|------------------------------------------|----|

|   |            | 4.2.3.1 1 <sup>st</sup> simulation       | 45 |

|   |            | 4.2.3.2 2 <sup>nd</sup> simulation       | 48 |

|   |            | 4.2.3.3 3 <sup>rd</sup> simulation       | 49 |

|   |            | 4.2.3.4 4 <sup>th</sup> simulation       | 51 |

|   |            | 4.2.3.5 5 <sup>th</sup> simulation       | 53 |

|   |            | 4.2.3.6 6 <sup>th</sup> simulation       | 54 |

|   |            | 4.2.3.7 7 <sup>th</sup> simulation       | 56 |

|   |            | 4.2.3.8 8 <sup>th</sup> simulation       | 58 |

|   |            | 4.2.3.9 9 <sup>th</sup> simulation       | 59 |

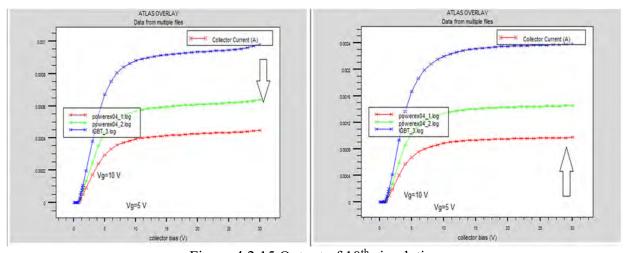

|   |            | 4.2.3.10 10 <sup>th</sup> simulation     | 61 |

|   |            | 4.2.3.11 11 <sup>th</sup> simulation     | 62 |

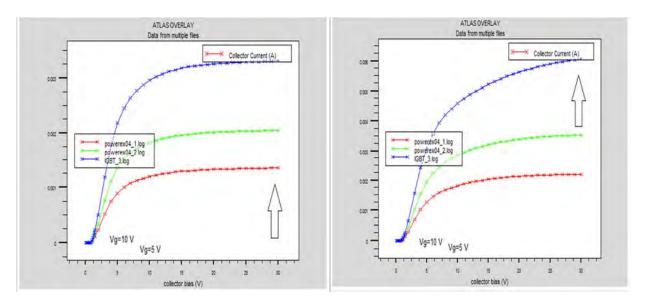

|   |            | 4.2.3.12 12 <sup>th</sup> simulation     | 64 |

| 5 | Result and | Discussion 66                            |    |

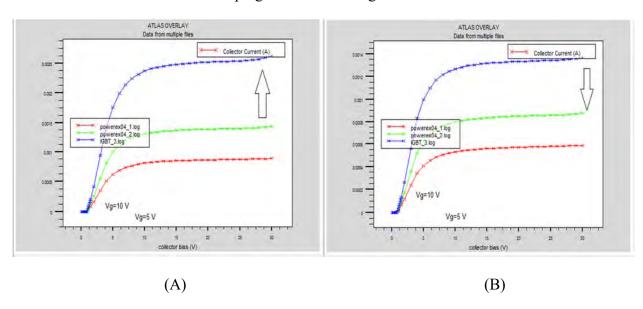

|   | 5.1 Simul  | ation comparing transfer characteristics | 66 |

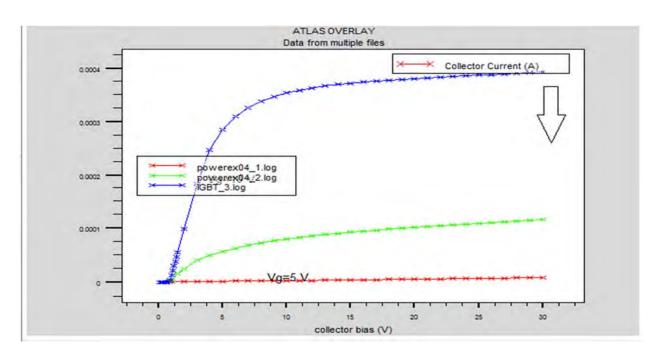

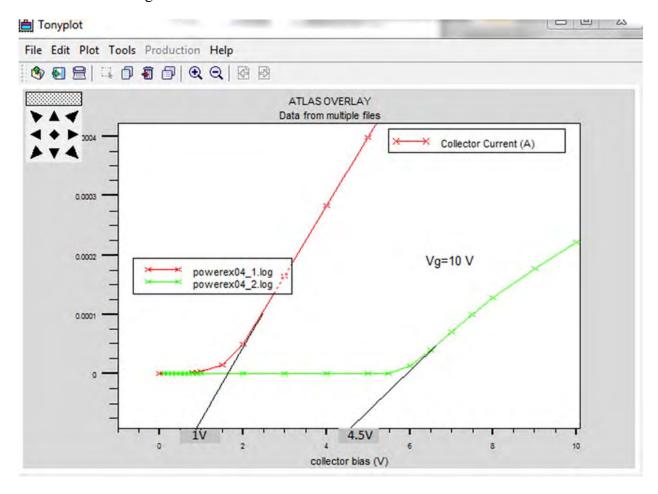

|   | 5.2 Simul  | ation comparing threshold voltage        | 69 |

| 6 | Conclusion | 71                                       |    |

# **List of Figures**

| l.l   | The power devices family, showing the principal power switches              | 5  |

|-------|-----------------------------------------------------------------------------|----|

| 2.1.1 | Schematic view of a Generic N-Channel IGBT                                  | 7  |

| 2.1.2 | NPT-IGBT and PT-IGBT                                                        | 8  |

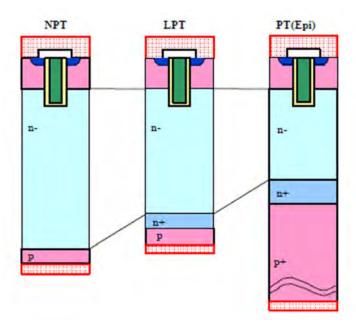

| 2.1.3 | Cross Sectional Structure of (a) NPT IGBT & (b) PT IGBT                     | 9  |

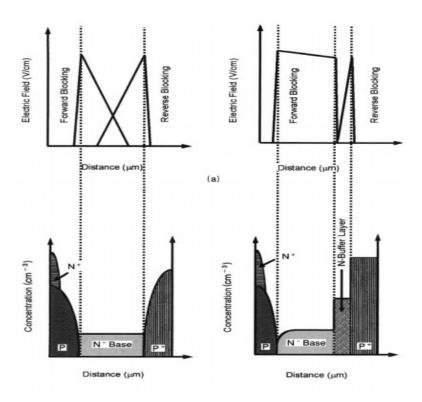

| 2.1.4 | Doping Concentration & Electric Field Distribution a) NPT IGBT & b) PT IGBT | 9  |

| 2.1.5 | The equivalent circuit model of IGBT                                        | 10 |

| 2.3.1 | Circuit Diagram of an IGBT                                                  | 12 |

| 2.3.2 | Equivalent Circuit of the IGBT                                              | 12 |

| 2.3.3 | The Circuit symbol of IGBT                                                  | 13 |

| 2.4.1 | 1-D coordinate system used in the modeling of the NPT IGBT                  | 17 |

| 2.4.2 | Typical IGBT turn-off transient showing turn-off phases (1 &2)              | 21 |

| 2.5.1 | Unit cell comparison.                                                       | 23 |

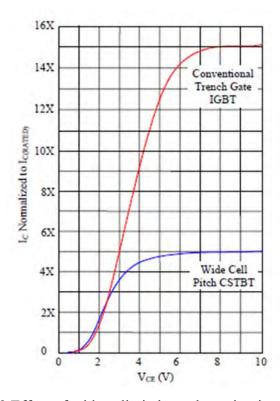

| 2.5.2 | Effect of wide cell pitch on short circuit saturation current               | 24 |

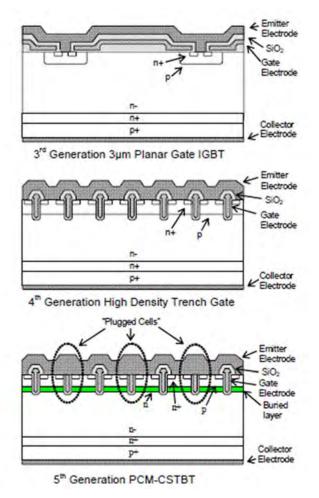

| 2.5.3 | IGBT surface structure comparison                                           | 25 |

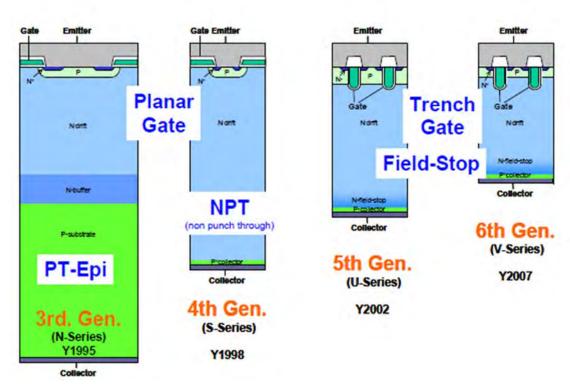

| 2.5.4 | IGBT vertical Structure comparison                                          | 26 |

| 2.5.5 | Transition of technologies applied to IGBT chips (1200volts)                | 27 |

| 3.2.1 | The collector base depletion capacitance formation                          | 30 |

| 3.2.2 | A comparison of the theoretical and measured 10A infinite inductive load    |    |

|       | switching voltage waveforms for devices with different base lifetimes       | 34 |

| 3.2.3 | The Excess carrier.                                                         | 35 |

| 3.2.4 | The carrier distribution in the base                                        | 37 |

| 4.1.1 | Interaction with ATLAS software                                             | 40 |

| 4.1.2  | Elements of ATLAS input deck in correct order                              | 41 |

|--------|----------------------------------------------------------------------------|----|

| 4.2.1  | Mesh of Trench IGBT                                                        | 42 |

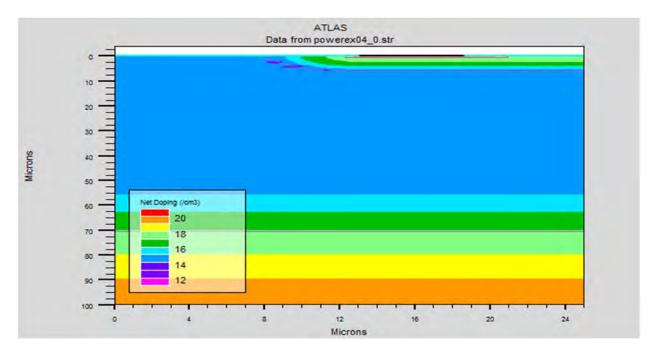

| 4.2.2  | N-(Drift region) with Trench gate                                          | 43 |

| 4.2.3  | Emitter Region                                                             | 44 |

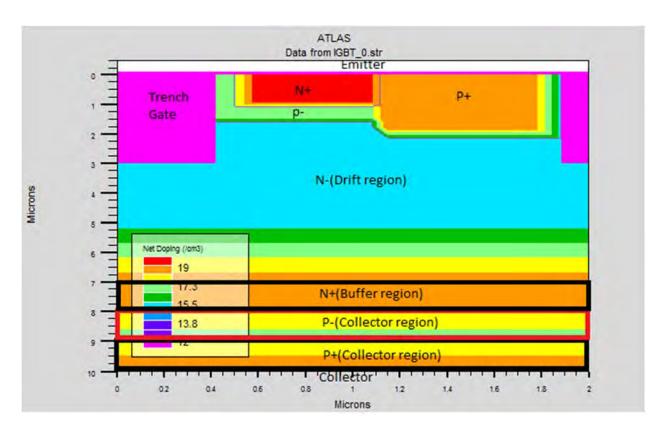

| 4.2.4  | Trench IGBT designed full model                                            | 45 |

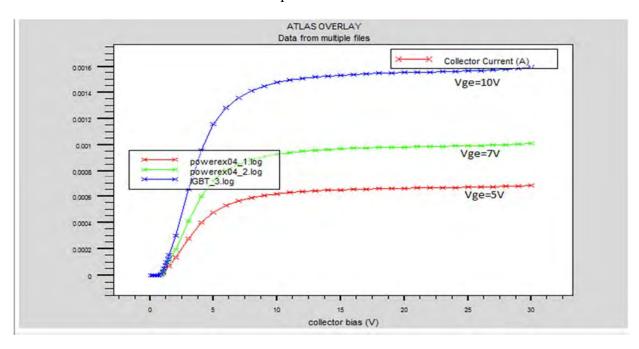

| 4.2.5  | Output of 1 <sup>st</sup> simulation                                       | 46 |

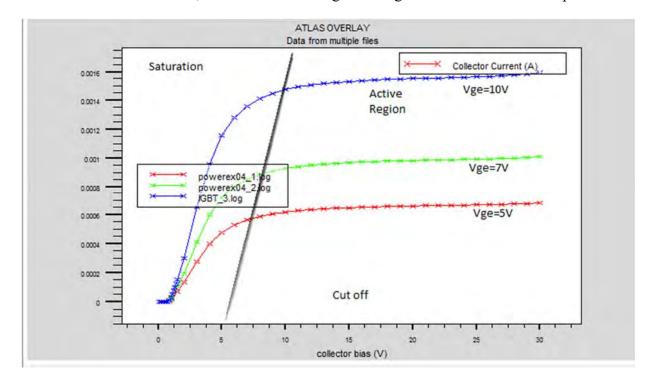

| 4.2.6  | Saturation, active and cutoff region of Trench IGBT                        | 47 |

| 4.2.7  | Output of 2 <sup>nd</sup> simulation                                       | 48 |

| 4.2.8  | Output of 3 <sup>rd</sup> simulation                                       | 50 |

| 4.2.9  | Output of 4 <sup>th</sup> simulation                                       | 52 |

| 4.2.10 | Output of 5 <sup>th</sup> simulation                                       | 53 |

| 4.2.11 | Output of 6 <sup>th</sup> simulation                                       | 55 |

| 4.2.12 | Output of 7 <sup>th</sup> simulation                                       | 57 |

| 4.2.13 | Output of 8 <sup>th</sup> simulation                                       | 58 |

| 4.2.14 | Output of 9 <sup>th</sup> simulation                                       | 60 |

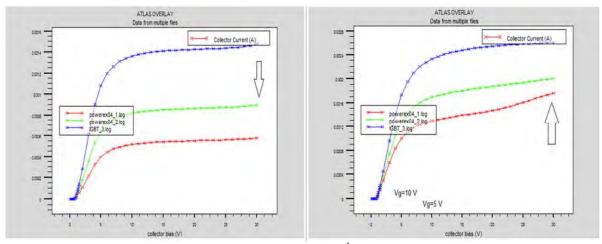

| 4.2.15 | Output of 10 <sup>th</sup> simulation                                      | 61 |

| 4.2.16 | Output of 11 <sup>th</sup> simulation                                      | 63 |

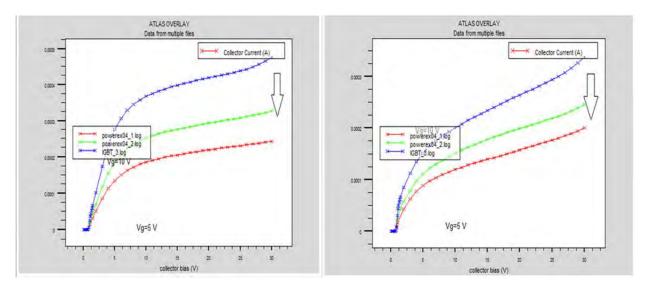

| 4.2.17 | Output of 12 <sup>th</sup> simulation                                      | 65 |

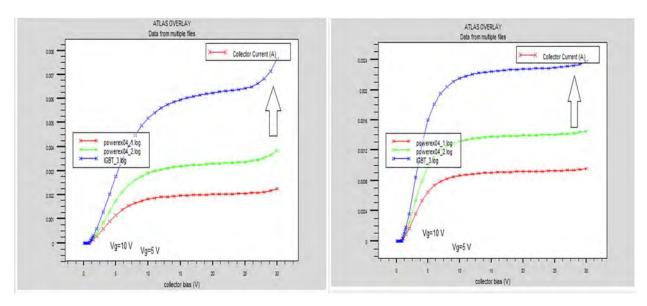

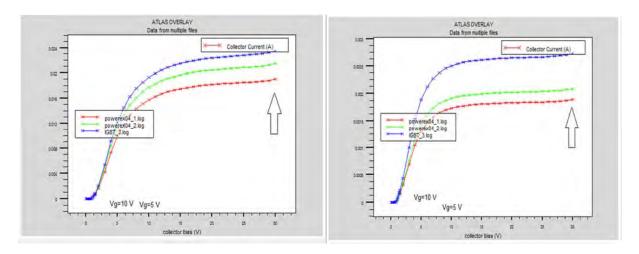

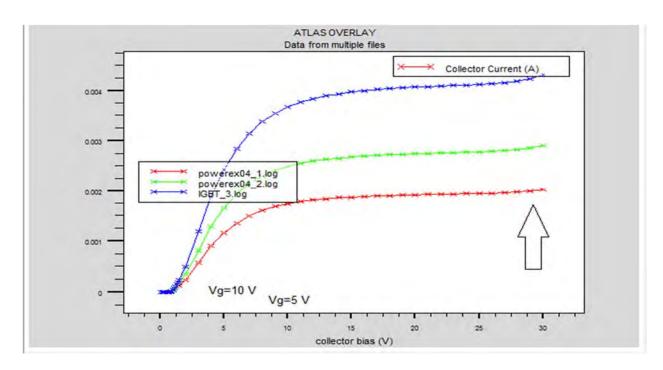

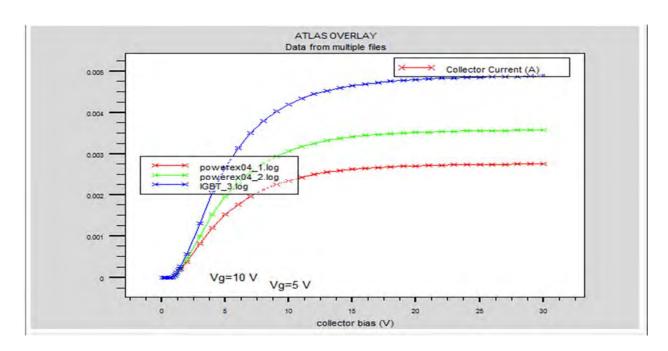

| 5.1.1  | Comprehensive model of PT-IGBT                                             | 67 |

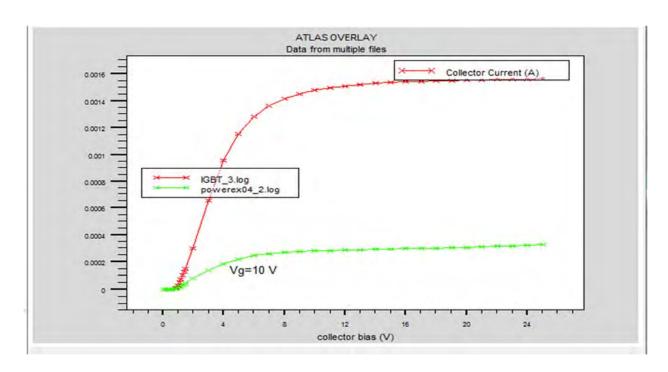

| 5.1.2  | Comparison of transfer characteristics with Traditional Punch through IGBT | 68 |

| 5210   | Comparison of threshold voltage with Traditional Punch through IGBT        | 69 |

## **List of Tables**

| 1.1    | Characteristics comparison of IGBT            | 3  |

|--------|-----------------------------------------------|----|

| 1.1.1  | Comparison among MOSFET, IGBT and BJT         | 4  |

| 2.1.2  | Difference between NPT-IGBT and PT-IGBT       | 10 |

| 2.5.1  | IGBT generation comparison                    | 22 |

| 4.2.1  | Set parameters for 1 <sup>st</sup> simulation | 46 |

| 4.2.2  | Ic vs Vce 1 <sup>st</sup> simulation output   | 47 |

| 4.2.3  | Set parameters for 2 <sup>nd</sup> simulation | 48 |

| 4.2.4  | Ic vs Vce 2 <sup>nd</sup> simulation output   | 49 |

| 4.2.5  | Set parameters for 3 <sup>rd</sup> simulation | 49 |

| 4.2.6  | Ic vs Vce 3 <sup>rd</sup> simulation output   | 50 |

| 4.2.7  | Set parameters for 4 <sup>th</sup> simulation | 51 |

| 4.2.8  | Ic vs Vce 4 <sup>th</sup> simulation output   | 52 |

| 4.2.9  | Set parameters for 5 <sup>th</sup> simulation | 53 |

| 4.2.10 | Ic vs Vce 5 <sup>th</sup> simulation output   | 54 |

| 4.2.11 | Set parameters for 6 <sup>th</sup> simulation | 54 |

| 4.2.12 | Ic vs Vce 6 <sup>th</sup> simulation output   | 55 |

| 4.2.13 | Set parameters for 7 <sup>th</sup> simulation | 56 |

| 4.2.14 | Ic vs Vce 7 <sup>th</sup> simulation output   | 57 |

| 4.2.15 | Set parameters for 8 <sup>th</sup> simulation | 58 |

| 4.2.16 | Ic vs Vce 8 <sup>th</sup> simulation output   | 59 |

| 4.2.17 | Set parameters for 9 <sup>th</sup> simulation | 59 |

| 4.2.18 | Ic vs Vce 9 <sup>th</sup> simulation output   | 60 |

| 4.2.19 | Set parameters for 10 <sup>th</sup> simulation | 62 |

|--------|------------------------------------------------|----|

| 4.2.20 | Ic vs Vce 10 <sup>th</sup> simulation output   | 62 |

| 4.2.21 | Set parameters for 11 <sup>th</sup> simulation | 61 |

| 4.2.22 | Ic vs Vce 11 <sup>th</sup> simulation output   | 63 |

| 4.2.23 | Set parameters for 12 <sup>th</sup> simulation | 64 |

| 4.2.24 | Ic vs Vce 11 <sup>th</sup> simulation output   | 65 |

| 5.1.1  | Set parameters for proposed trench PT-IGBT     | 66 |

| 5.1.2  | Set parameters for traditional PT-IGBT         | 67 |

| 5.1.3  | Transfer characteristics comparison output     | 68 |

| 5.2.1  | Threshold voltage comparison output            | 70 |

## **Abbreviations**

| IGBT     | Insulated Gate Bipolar Transistor                   |

|----------|-----------------------------------------------------|

| BJT      | Bipolar Junction Transistor                         |

| MOSFET   | Metal Oxide Semiconductor Field Effect Transistor   |

| VDMOSFET | Vertical Double diffused MOSFET                     |

| PT IGBT  | Punch Through Insulated Gate Bipolar Transistor     |

| NPT IGBT | Non Punch Through Insulated Gate Bipolar Transistor |

| VFD      | Variable frequency Drive                            |

| GEMFET   | Gain Enhanced MOSFET                                |

| COMFET   | Conductivity Modulated FET                          |

| BiFET    | Bipolar FET                                         |

| PWM      | Pulse Width Modulation                              |

| UPS      | Uninterruptable power Supply                        |

| DMOS     | Depletion MOSFET                                    |

| JFET     | Junction gate Field Effect Transistor               |

| RTC      | Real Time Control                                   |

| PCM      | Plugged Cell Merged                                 |

## **Physical Constants**

| Ambipolar Diffusivities | D = | $18 \text{ cm}^2/\text{s}$ |

|-------------------------|-----|----------------------------|

|-------------------------|-----|----------------------------|

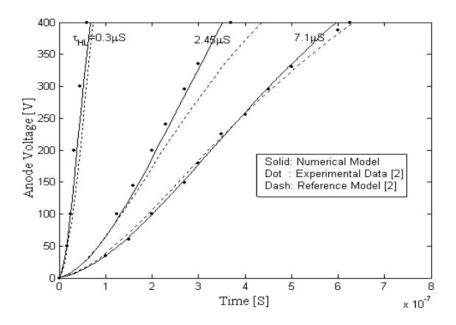

High level excess carrier lifetime  $\tau_{HL} = 0.1 \,\mu s \,(\tau_0)$

$= 0.3 \, \mu s \, (\tau_1)$

$= 2.45 \,\mu s \,(\tau_2)$

$= 7.1 \,\mu s \,(\tau_3)$

Supply voltage  $V_{bus} = 400 \text{ V}$

Dielectric constant of Si  $\varepsilon_{Si} = 11.7 \times 8.854 \times 10^{-14} \, \text{F/cm}$

Charge of electron  $q = 1.6 \times 10^{-19} \,\mathrm{C}$

Base doping concentration  $N_B = 2 \times 10_{14} \,\mathrm{cm}$ -3

Hole Diffusivity  $D_p = \frac{14 \text{ cm}^2}{\text{s}}$

Metallurgical base width  $W_B = 9.3 \times 10^{-3} \,\mathrm{cm}$

Device active area  $A = 0.1 \text{ cm}^2$

Emitter electron saturation current  $I_{sne} = 6 \times 10_{-14} \,\mathrm{A}$

Intrinsic carrier concentration  $n_i = 1.45 \times 10^{10} \, \text{cm}^{-3}$

Electron mobility  $\mu_n = \frac{1500 \text{ cm}^2}{V \text{ s}}$

Hole mobility  $\mu_p = 450 \text{ cm}^2/V s$

Ambipolar mobility ratio b = 3.3

Total current  $I_T = 10 \text{ A}$

## **Symbols**

| A                          | Device active area                   | $cm^{-3}$    |

|----------------------------|--------------------------------------|--------------|

| I n,Ip                     | electron hole current                | A            |

| $\delta p$                 | excess carrier concentration         | <i>cm</i> -3 |

| n, p                       | electron, hole carrier concentration | <i>cm</i> -3 |

| Q                          | total excess carrier base charge     | С            |

| $W_B$                      | metallurgical base width             | cm           |

| P <sub>0</sub>             | excess carrier concentration at x=0  | <i>cm</i> -3 |

| $\emptyset_n, \emptyset_p$ | electron,hole quasi-fermi potential  | V            |

| Е                          | electric field                       | V/cm         |

| Х                          | distance in base from emitter        | cm           |

| Q                          | electron charge                      | С            |

| $\mu_n, \mu_p$             | electron, hole mobility              | $cm^{-2}/Vs$ |

| $D_n$ , $D_p$              | electron, hole diffusivity           | $cm^{-2}/s$  |

| THL                        | high level excess carrier lifetime   | S            |

| $I_T = I_n + I_p$          | Total current                        | A            |

| $b = \frac{\mu_n}{\mu_p}$  | ambipolar mobile ratio               | -            |

| D                          | ambipolar diffusivity                | $cm^{-2}/s$  |

| L                          | ambipolar diffusion length           | cm           |

## Chapter 1

## **Introduction**

An Insulated-Gate Bipolar Transistor (IGBT) is a three-terminal power semiconductor device primarily used as an electronic switch which, as it was developed, came to combine high efficiency and fast switching. Since it is designed to turn on and off rapidly, amplifiers that use it often synthesize complex waveforms with pulse-width modulation and low-pass filters. In switching applications modern devices feature pulse repetition rates well into the ultrasonic range—frequencies which are at least ten times the highest audio frequency handled by the device when used as an analog audio amplifier.

The IGBT transistor takes the best parts of two types of transistors, the high input impedance and high switching speeds of a MOSFET with the low saturation voltage of a bipolar transistor, and combines them together to produce another type of transistor switching device that is capable of handling large collector-emitter currents with virtually zero gate current drive. The Insulated Gate Bipolar Transistor, (IGBT) combines the insulated gate (hence the first part of its name) technology of the MOSFET with the output performance characteristics of a conventional bipolar transistor, (hence the second part of its name). The result of this hybrid combination is that the "IGBT Transistor" has the output switching and conduction characteristics of a bipolar transistor but is voltage-controlled like a MOSFET.

IGBTs are mainly used in power electronics applications, such as inverters, converters and power supplies, were the demands of the solid state switching device are not fully met by power bipolar and power MOSFETs. High-current and high-voltage bipolar are available, but their switching speeds are slow, while power MOSFETs may have higher switching speeds, but high-voltage and high-current devices are expensive and hard to achieve. IGBT has many others

applications also such as variable frequency drives (VFDs), electric cars, trains, variable speed refrigerators, lamp ballasts, air-conditioners and even stereo systems with switching amplifiers.

#### The main advantages of IGBT over a Power MOSFET and a BJT are

- ➤ It has a very low on-state voltage drop due to conductivity modulation and has superior on-state current density. So smaller chip size is possible and the cost can be reduced.

- ➤ It offers greater power gain than the standard bipolar type transistor combined with the higher voltage operation and lower input losses of the MOSFET. In effect it is an FET integrated with a bipolar transistor in a form of Darlington type configuration.

- ➤ Wide SOA: It has superior current conduction capability compared with the bipolar transistor. It also has excellent forward and reverse blocking Capabilities.

- It has lower on-state and switching losses and also lowers thermal impedance.

- Low driving power and a simple drive circuit due to the input MOS gate structure. It can be easily controlled as compared to current controlled devices (thyristor, BJT) in high voltage and high current applications.

#### Main drawbacks are:

- The switching frequency of insulated gate bipolar transistor (IGBT) is not as high as that of a power MOSFET. The collector current following due to the minority charge carriers roots the turnoff speed to be slow.

- ➤ It cannot block high reverse voltages.

- There is a chance of latch up due to the internal structure of PNPN thyristor.

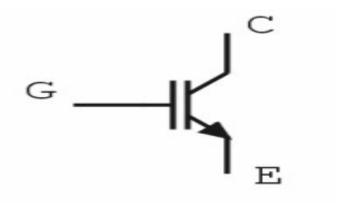

We can see that the insulated gate bipolar transistor is a three terminal, transconductance device that combines an insulated gate N-channel MOSFET input with a PNP bipolar transistor output connected in a type of Darlington configuration. As a result the terminals are labelled as: **Collector**, **Emitter** and **Gate**. Two of its terminals (C-E) are associated with the conductance path which passes current, while its third terminal (G) controls the device

|                       | IGBT Compa                              | rison Table [1]                  |                                 |

|-----------------------|-----------------------------------------|----------------------------------|---------------------------------|

| Device Characteristic | Power Bipolar                           | Power MOSFET                     | IGBT                            |

| Voltage Rating        | High <1kV                               | High <1kV                        | Very High >1kV                  |

| Current Rating        | High <500A                              | High > 500A                      | High >500A                      |

| Input Drive           | Current ratio h <sub>FE</sub><br>20-200 | Voltage V <sub>GS</sub><br>3-10V | Voltage V <sub>GE</sub><br>4-8V |

| Input Impedance       | Low                                     | High                             | High                            |

| Output Impedance      | Low                                     | Medium                           | Low                             |

| Switching Speed       | Slow (µs)                               | Fast (ns)                        | Medium                          |

| Cost                  | Low                                     | Medium                           | High                            |

Table 1.1 Characteristics comparison of IGBT

.An insulated gate bipolar transistor is simply turned "ON" or "OFF" by activating and deactivating its Gate terminal. Applying a positive input voltage signal across the Gate and the Emitter will keep the device in its "ON" state, while making the input gate signal zero or slightly negative will cause it to turn "OFF" in much the same way as a bipolar transistor or a MOSFET.

#### 1.1 Device Evolution: BJT, MOSFET and IGBT

The bipolar transistor was the only "real" power transistor until the MOSFET came along in the 1970's. The bipolar transistor requires a high base current to turn on, has relatively slow turnoff characteristics (known as current tail), and is liable for thermal runaway due to a negative temperature co-efficient. In addition, the lowest attainable on-state voltage or conduction loss is governed by the collector-emitter saturation voltage  $V_{\text{CE(SAT)}}$ .

The MOSFET, however, is a device that is voltage- and not current-controlled. MOSFETs have a positive temperature co-efficient, stopping thermal runaway. The on-state-resistance has no theoretical limit; hence on-state losses can be far lower. The MOSFET also has a body-drain

diode, which is particularly useful in dealing with limited freewheeling currents. All these advantages and the comparative elimination of the current tail soon meant that the MOSFET became the device of choice for power switch designs.

Then in the 1980s the IGBT came along. The IGBT is a cross between the bipolar and MOSFET transistors. Early versions of the IGBT are also prone to latch up, but nowadays, this is pretty well eliminated. Another potential problem with some IGBT types is the negative temperature co-efficient, which could lead to thermal runaway and makes the paralleling of devices hard to effectively achieve. This problem is now being addressed in the latest generations of IGBTs that are based on "non-punch through" (NPT) technology. This technology has the same basic IGBT structure but is based on bulk-diffused silicon, rather than the epitaxial material that both IGBTs and MOSFETs have historically used.

| Characteristics                        | MOSFET                                      | IGBT                                                           | ВЈТ                                                           |

|----------------------------------------|---------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------|

| Type of drive                          | voltage                                     | voltage                                                        | current                                                       |

| Drive power                            | Minimal                                     | Minimal                                                        | Large                                                         |

| Drive complexity                       | simple                                      | simple                                                         | High (large positive and negative currents required)          |

| Current density for given voltage drop | High at low voltage.  Low at high voltages. | Very high(small tradeoff with switching speed)                 | Medium (severe trade-off with switching speed)                |

| Switching losses                       | Very low                                    | Low to medium (depending on trade- off with conduction losses) | Medium to high (depending on tradeoff with conduction losses) |

Table 1.1.1 Comparison among MOSFET, IGBT and BJT

#### 1.2 Advent of IGBTs

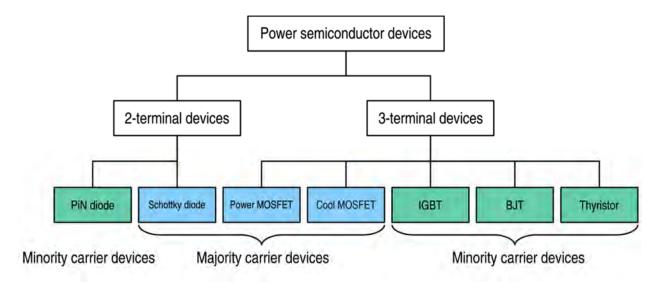

Insulated Gate Bipolar Transistor (IGBT) emerged to be the milestone breakthrough in the sphere of power semiconductor devices. Figure 1.1 gives a general classification overview of all the traditional power semiconductor devices found in today's technology.

Figure 1.1 the power devices family, showing the principal power switches

IGBT was demonstrated for the first time by Baliga in 1979 Over the years it has been referred to by numerous other names which includes Insulated Gate Rectifier (IGR), Conductivity-Modulated FET (COMFET), Gain-Enhanced MOSFET (GEMFET), Bipolar FET (BiFET) and Injector FET. It became commercially available in 1983.

IGBTs are inherently a minority carrier device where the current conduction takes place through both the majority and minority carriers of the semiconductor material it is composed of. It is generally viewed as a device with MOS input characteristics and bipolar output characteristics that is a voltage-controlled bipolar device. Indeed, in principle, it has a very high input impedance and large bipolar current-carrying capability thus allowing the users to combine the advantages of Power MOSFET and BJT into a single monolithic device.

IGBTs have found numerous applications in various power electronic systems, especially in Pulse Width Modulated (PWM) servo and three-phase drives requiring high dynamic range control and low noise. It is also an essential component in Uninterruptible Power Supplies (UPS), Switched-Mode Power Supplies (SMPS), and other power circuits requiring high switch repetition rates. IGBT improves dynamic performance and efficiency and reduces the level of audible noise. It is equally suitable in resonant-mode converter circuits. Optimized IGBT is available for both low conduction loss and low switching loss.

## **Chapter 2**

## **Basic Principles of IGBT**

#### 2.1 Basic Structure of IGBT

#### 2.1.1 Cross Sectional Structure of IGBT

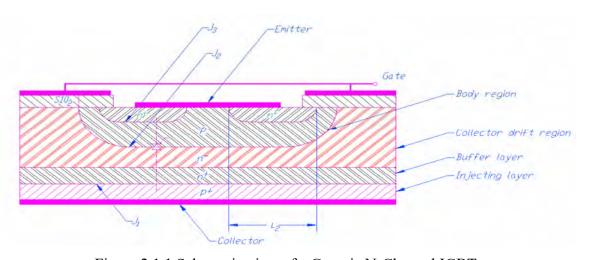

The basic schematic of a typical N-channel IGBT build on DMOS process that shown in Figure 2.1. This is one of many structures possible for this device. It is noticeable that the silicon cross section of an IGBT is almost identical of that of a vertical Power MOSFET except for the P+ injecting layer. It shares similar MOS gate structure and P wells with N+ source regions. At the top N+ layer is the source or emitter and at the bottom P+ layer is the drain or collector. It is also achievable to make P-channel IGBTs and which the doping profile in each layer will be reversed. IGBT has a parasitic thyristor comprising the four-layer NPN structure. Turn on of this thyristor is undesirable. There are different types of IGBT which are manufactured without the N+ buffet layer they are called non-punch through (NPT) IGBTs whereas those with this layer are called punch-through (PT) IGBTs. The presence of this buffer layer can significantly improve the performance of the device if the doping level and thickness of this layer are chosen appropriately.

Figure 2.1.1 Schematic view of a Generic N-Channel IGBT

Despite physical similarities, the operation of an IGBT is closer to that of a power BJT than a power MOSFET. It is due to the drain layer (injecting layer) which is responsible for the minority carrier injection into the N-drift region and the resulting conductivity modulation.

#### 2.1.2 NPT-IGBT and PT-IGBT

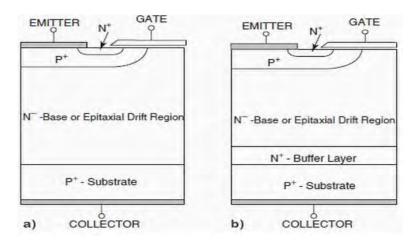

The NPT and PT-IGBT's are developed by IXYS Corporation. The physical construction of the NPT and PT IGBTs are shown in figure 2.1.2. The structure of PT consists of an extra buffer layer that executes two functions they are, 1) the failure can be avoided by punch through action as the depletion area expansion at applied high voltage is controlled by this layer. 2) Fail current can be reduced when it turns off & reduces the fall time of the IGBT because the holes are inserted by the collector of the P+ incompletely recombine in this layer.

Figure 2.1.2 NPT-IGBT and PT-IGBT

The basics of NPT-IGBT, IXYS Corporation 4 IXAN0063 and Abdus Sattar have equal breakdown voltage and these are applicable for AC applications. The PT-IGBTs have less breakdown voltage and these are relevant for DC circuits where these devices are not essential to support voltage in the reverse direction.

Figure 2.1.3 Cross Sectional Structure of (a) NPT IGBT & (b) PT IGBT

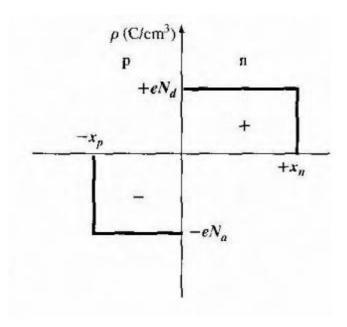

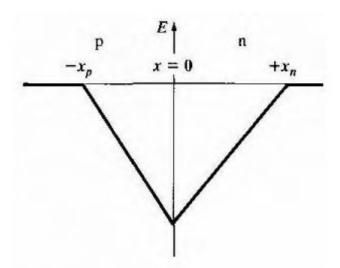

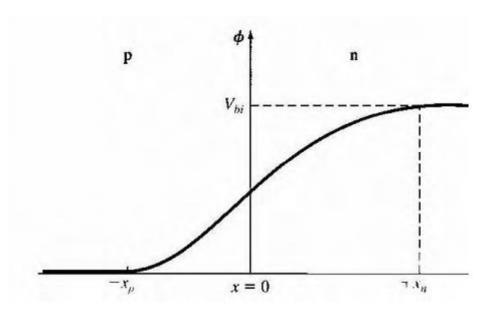

The NPT IGBTs, which have equal forward and reverse breakdown voltage, are suitable for AC applications. The PT IGBTs, which have less reverse breakdown voltage than the forward breakdown voltage, are applicable for DC circuits where devices are not required to support voltage in the reverse direction. Fig. 2.1.4 shows the Doping Concentration & Electric Field distribution of NPT & PT IGBT.

Figure 2.1.4 Doping Concentration & Electric Field Distribution (a) NPT IGBT & (b) PT IGBT

Figure 2.1.5 the equivalent circuit model of IGBT

#### 2.1.3 Difference between NPT-IGBT and PT-IGBT

It is a voltage controlled device and it needs a small amount of voltage on the gate terminal to keep conduction through the device. This is a unidirectional device because, it can only change current in the forward direction that is collector-to-emitter.

|                         | NPT                                                                                               | Low Short tail current Significant increase in E <sub>off</sub> with temperature |  |

|-------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| Switching Loss          | Medium  Long, low amplitude tail current.  Moderate increase in E <sub>off</sub> with temperature |                                                                                  |  |

| Conduction Loss         | Medium<br>Increases with temperature                                                              | Low Flat to slight decrease with temperature                                     |  |

| Paralleling             | Easy Optional sorting Recommend share heat                                                        | Difficult<br>Must sort on V <sub>CE(on)</sub>                                    |  |

| Short-Circuit Rated Yes |                                                                                                   | Limited<br>High gain                                                             |  |

Table 2.1.2 Difference between NPT-IGBT and PT-IGBT

The principle of the BJTs is very similar to the N-channel MOSFET. The main difference is, the current existing by the conducting channel when current supplies through the device in its ON state is very small in the IGBT, due to this reason, the ratings of the currents are high when matched with an MOSFET.

#### 2.2 Switching Behavior of IGBT

These devices are mostly used as switches, for instance frequency converter and chopper applications, the variation of a diode is most important, because when the switching of the IGBT is OFF, then the current is determined by the load that is inductive in many cases.

By connecting appropriate diodes, the current flow is allowed. When this transistor is switched on again, the current flowing in a diode at first works like a short. The voltage can be blocked by removing the stored voltage. This looks as a surplus current added to the load current which is called as the reverse recovery current of the diode 'Irr'. The max of Irr occurs (di/dt = 0) when the amount of the sudden voltages through the IGBT & the diode matches the supply voltage. When the IGBT is turned ON, then the current changes which make an over-voltage point by the change in the current in the dependent inductances agreeing to  $\Delta VCE = L\sigma \times di/d$

### 2.3 Principles of Operation of IGBT

### 2.3.1 Circuit Diagram of IGBT

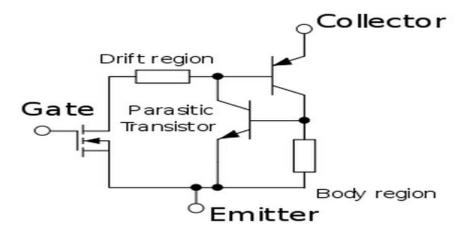

Based on the basic structure of the IGBT, a simple circuit can be drawn using PNP and NPN Transistors, JFET, MOSFET, that is shown in the below figure 2.3.1 The collector terminal of the NPN transistor is connected to the base terminal of the PNP via JFET transistor. These transistors signify the parasitic thyristor which creates a regenerative feedback loop. The RB resistor signifies the shorting of the base-emitter terminals of the NPN transistor to ensure that the thyristor doesn't latch up that will lead to the IGBT latch-up.

Figure 2.3.1 Circuit Diagram of an IGBT

The JFET transistor signifies the construction of current b/n any two adjacent IGBT cells. It allows the MOSFET and supports most of the voltage. A circuit symbol for the IGBT is shown below, that consists of three terminals namely emitter, gate and collector.

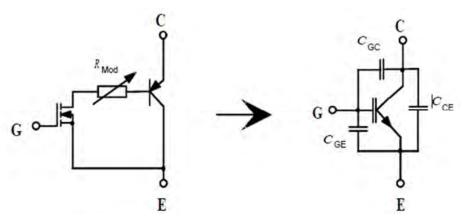

### 2.3.2 Equivalent Circuit of IGBT

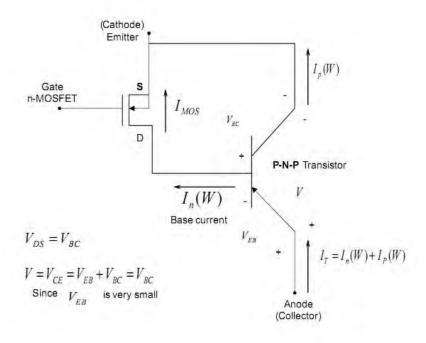

The equivalent circuit of the IGBT can be depicted quite accurately by a pnp-transistor, where the base current is controlled by a MOS transistor. The conductivity of the resistor on the base branch is increased (modulated) when the IGBT is turned-on. This way, the greater part of the load current is flowing over the base branch. These effects only show for the user by a turn-on delay time and a tail current at turn-off. For this reason, the device can be simply considered as a MOS transistor with the corresponding capacities.

Figure 2.3.2 Equivalent Circuit of the IGBT

Based on the structure, an equivalent circuit of IGBT can be shown in Fig. 2.3.3 It consists of a PNP transistor (BJT) & an n-channel MOSFET. The  $p^+$  substrate,  $n^-$  epilayer &  $p^+$  body forms the PNP transistor. The p-type substrate is the emitter for BJT and is the anode terminal of the device. When the p substrate is forward biased ( $V_{EB}$ =0), the minority carrier injection causes transistor current  $I_T$ , flowing from the anode region.

This current has two parts at the Base-

- Electron current  $(I_n(W))$ .

- Hole current  $(I_p(W))$ .

The Anode to Cathode voltage  $(V_{AC})$  can be represented by

$$V_{AC} = V_{EB} + V_{BC}$$

Where,

Figure 2.3.3 The Circuit symbol of IGBT

$V_{EB}$ =Bipolar Emitter to Base voltage.

$V_{BC}$ =Base to Cathode voltage.

Basically  $V_{DS}$  of MOSFET &  $V_{BC}$  are same. Since  $V_{EB}$  is very small, we can write

$$V_{AC} = V_{BC}$$

From the equivalent circuit, a circuit symbol can be formed which is shown in Fig. 2.3.3 It has three parts-

- Collector (C) which is the anode terminal of IGBT.

- Gate (G) which is the Gate terminal of MOSFET.

- Emitter (E) which is the cathode terminal of IGBT

#### 2.3.3 IGBT Operation

When a positive gate voltage greater than the threshold voltage  $(V_T)$  is applied, electrons are attracted from the  $p^+$  body towards the surface under the gate. These attracted electrons will invert the  $p^+$  body region directly under the gate to form an n channel.

A path is formed for charges to flow between the  $n^+$  source and the  $n^-$  drift region.

When a positive voltage is applied to the anode terminal of the IGBT, the emitter of the IGBT section is at higher voltage than collector. Minority carriers (holes) are injected from the emitter  $(p^+ \text{ region})$  into the base  $(n^- \text{ drift region})$ . As the positive bias on the emitter of the BJT part of the IGBT increases, the concentration of the injected hole increases as well. The concentration of the injected holes will eventually exceed the background doping level of the  $n^- \text{ drift region}$ ; hence the conductivity modulation phenomenon. The injected carriers reduce the resistance of the  $n^- \text{ drift region}$  and, as a result, the injected holes are recombined with the electrons flowing from the source of the MOSFET to produce the anode current (on state).

When a negative voltage is applied to the anode terminal, the emitter-base junction is reversed biased and the current is reduced to zero. A large voltage drop appears in the  $n^-$  drift region since the depletion layer extends mainly into that region.

The MOSFET gate voltage controls the IGBT switching action. The turn-OFF takes place when the gate voltage is less than the threshold voltage ( $V_T$ ). The inversion layer at the surface of the  $p^+$  body under the gate cannot be kept and therefore no electron current is available in the

MOSFET channel while the remaining minority carriers of holes, which were stored during the on state of the IGBT, require some time in order to be removed or extracted.

The switching speed of the IGBT device depends upon the time it takes for the removal of the stored charges in the  $n^-$  drift region which were built up during the on state current conduction (IGBT tern-on case).

#### 2.4 Basic Tools for Operation

The Physics-based modeling approach is used in this discussion to better understand the effect of the carriers on the IGBT characteristics. The following points have to be taken into account in performing the analysis.

• The carrier distribution in the n-drift region of the IGBT is described by the ambipolar diffusion equation because of the high level injection of holes in this region  $(p(x) >> N_B)$

$$\frac{\partial^2 p(x)}{\partial x^2} = \frac{p(x)}{L^2} + \frac{1}{D} \frac{\partial p(x)}{\partial x}$$

Where,

- ➤ N<sub>B</sub>= Base background doping concentration

- $\triangleright$  P(x)= Hole concentration

- > D= Ambipolar diffusion constant

- > T<sub>HL</sub>= Hole carrier lifetime

- $L = \sqrt{D\tau_{HL}}$ =Bipolar diffusion length

- Transport of the bipolar charge is assumed to be one-dimensional (1-D) for the ease of analysis.

- The emitter region of the BJT part of the IGBT has a very high doping concentration level  $(p^+ >> 10^{18} cm^{-3})$ . This region acts like recombination centers for minority carriers coming from the lightly doped base region (electron in this case).

The space charge region, which is depleted of minority carriers, supports the entire voltage drop across the collector-base terminals based on Poisson's equation. The effect of mobile carriers in the depletion region is not accounted for in this dissertation.

#### 2.4.1 The Steady State Operation

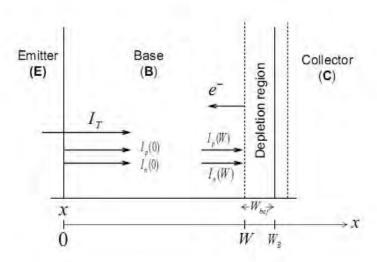

The equivalent circuit model and 1-D coordinate system of Fig. 2.6 is used in the modeling approach of the NPT IGBT analysis. From this figure,  $I_T$  is the IGBT total current,  $I_p$  is the hole current of the BJT and  $I_n$  is the base or MOS electron current.

*I<sub>T</sub>* can be expressed in several ways:

$$I_T = I_p(x=0) + I_n(x=0)$$

(2.1)

$$I_T = I_p(x = W) + I_n(x = W)$$

(2.2)

$$I_T = I_p(x) + I_n(x) \tag{2.3}$$

The IGBT operates under low gain and high level injection conditions.

The current equations are as

$$J_n = nq\mu_n E + qD_n \frac{\partial n(x)}{\partial x} \qquad (2.4)$$

$$J_{n} = nq\mu_{n}E + qD_{n}\frac{\partial n(x)}{\partial x}$$

$$J_{p} = pq\mu_{p}E - qD_{p}\frac{\partial p(x)}{\partial x}$$

(2.4)

$$(2.5)$$

Figure 2.4.1 1-D coordinate system used in the modeling of the NPT IGBT

where  $J_n$  is the electron current &  $J_p$  is the hole current

The first terms in equations 2.4 & 2.5 are due to drift component while the second terms are due to diffusion component.

When the excess carrier concentration is larger than the background concentration the transport of electrons and holes are coupled by the electric field in the drift terms of the transport equations. The minority carrier current density  $J_n$  cannot be neglected and ends up affecting the majority carrier current density  $J_p$ . Hence equations 2.4 & 2.5 cannot be coupled. The total current density is given by

$$J_T = J_n + J_p$$

$$= (nq\mu_n + pq\mu_p)E + q\left(D_n \frac{\partial n(x)}{\partial x} - D_p \frac{\partial p(x)}{\partial x}\right)$$

substituting for the electric field from the equations 2.4 yields

$$J_n = \left[\frac{nq\mu_n}{nq\mu_n + pq\mu_p}\right] J_T + q \frac{\partial n}{\partial x} \left[\frac{nq\mu_n D_p + pq\mu_p D_n}{nq\mu_n + pq\mu_p}\right]$$

An ambipolar diffusion coefficient D is defined as

$$D = \frac{nq\mu_n D_p + pq\mu_p D_n}{nq\mu_n + pq\mu_p}$$

The expression for  $J_n$  can be rearranged & rewritten as

$$J_n = \left[\frac{b}{1+b}\right] J_T + qD \frac{\partial n}{\partial x} \tag{2.6}$$

where  $b=\mu_n/\mu_p$

Repeating the same procedure starting with equation (2.6),  $J_p$  is obtained

$$J_p = \left[\frac{1}{1+b}\right] J_T - qD \frac{\partial p}{\partial x} \tag{2.7}$$

where  $J_T$  is the total current density= $J_n+J_p$  & assuming n=p

The excess hole carrier distribution p(x) can be obtained by solving the steady state hole continuity equation

$$\frac{\partial^2 p(x)}{\partial x^2} = \frac{p(x)}{L^2} \tag{2.8}$$

Considering the coordinate system given in Fig. 2.4.1, the boundary conditions for the excess hole carrier distribution are

$$p(x = 0) = P_0$$

(2.9)  $p(x = W) = 0$  (2.10)

Equation (2.10) results from the collector-base junction being reversed biased for forward condition and equation (2.10) reflects that emitter-base junction is forward biased.

$P_0$  is the excess carrier concentration at x=0, W(t) is the quasi-neutral base width

given by

$$W = W_B - W_{bci}$$

(2.11)

where  $W_B$  is the metallurgical base width and  $W_bcj$  is the collector-base depletion width. We know, Poisson's equation

$$\frac{d^2V}{dx^2} = \frac{qN_B}{\varepsilon_{Si}} \qquad (2.12)$$

Solving Poisson's equation yields an expression for the collector-base junction depletion width as

$$W_{bcj} = \sqrt{\frac{2\varepsilon_{Si}V_{bc}}{qN_B}} \tag{2.13}$$

where  $N_B$  is the doping concentration of the lightly doped region of the IGBT and  $\varepsilon_{Si}$  is the dielectric constant of silicon. The junction voltage  $V_{bcj}$ =V= $V_{bc}$ + $V_{bi}$  is the collector base junction voltage drop of the BJT part of the IGBT and  $V_{bi}$  is the built in potential. Hence from Fig. 2.4.1

$$W = W_B - \sqrt{\frac{2\varepsilon_{Si}V}{qN_B}} \quad (2.14)$$

Where, V=V<sub>bc</sub>=V<sub>BE</sub>=V<sub>A</sub> is the collector base voltage that appears across the drift region.

### 2.4.2 The Transient State Operation

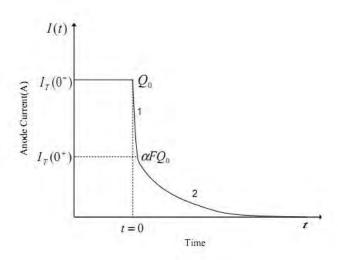

While the turn-on time of the IGBT is quite fast, the turn-off time can be slow because of the open base of the PNP transistor during the turn-off period. Fig. 2.4.2 shows the typical IGBT turn-off transient where  $I_T(0^+)$  is the current after the initial rapid fall. The initial rapid drop in the anode current is due to the sudden removal of the MOS channel. This is followed by a slower decay due to the removal of the carriers stored in the lightly doped layer( $n^-$ ). The turn-off process is initiated when we lower the gate voltage to a value lower than threshold voltage( $V_T$ )

(first phase). This removes the formed electron channel from under the gate and blocks the MOS component of the current  $I_{MOS}$ .  $I_{MOS}=I_n(W)=0$  in this case and the collector-base voltage  $V_{bc}$  increases resulting in a widening of the depletion region at the  $n^-$  (base-collector side or source of MOSFET).

The relation between  $I_T(0^-)$  and  $I_T(0^+)$  is through  $\beta_{tr}$ . It is the ratio of the current immediately after the initial rapid fall to the magnitude of the fall and is shown along with the ratio of W(t) to L (W(t)/L) in the appendices.

The switching losses of the IGBT are dominated by the losses, which occur during the much slower second phase of the turn-off period transient. This is because of the time required removing or extracting the injected carriers in this phase. This is a major disadvantage of the IGBT device as it suffers from high-switching losses. This can be overcome by reducing the lifetime of the carriers in the base through recombination of extraction processes quickly as possible before the device reaches its blocking voltage state.

The collector-base junction is reversed biased and its depletion region widens during the turn-off of the IGBT. When the IGBT is on, the status of the base-collector junction is reversed biased as can be seen from Fig. 2.1.5 When the IGBT is off, the status of the base-collector junction is reversed biased and  $V_{bc}$  is increased leading to the increment of the depletion region since the current decreases. The widened region supports the entire voltage drop across the device as mentioned previously based on

Figure 2.4.2 typical IGBT turn-off transient showing turn-off phases (1 &2)

Poisson's equation. Since the quasi-neutral base width of the IGBT changes with time and decreases with the increase of  $V_{bc}$ , we can find an expression for the rate of rise of the voltage across the device  $\frac{dV(t)}{dt}$  (varying of the output voltage) during the switching OFF of the IGBT from the collector-base junction depletion width  $W_{bcj}$  expression as shown. From  $W_{bcj} = \sqrt{\frac{2\varepsilon_{Si}V_{bc}(t)}{qN_B}}$  and the fact that  $W(t)=W_B-W_{bcj}(t)$  if we take the time derivative of  $W_{bcj}(t)$  we get,

$$\frac{dW_{bcj}(t)}{dt} = \sqrt{\frac{\varepsilon_{Si}}{2qN_BV(t)}} \frac{dV(t)}{dt}$$

and

$$\frac{dW(t)}{dt} = -\frac{dW_{bcj}(t)}{dt} = -\sqrt{\frac{\varepsilon_{Si}}{2qN_BV(t)}} \frac{dV(t)}{dt}$$

(2.15)

This equation shows the time rate of the change of the quasi-neutral base width (W(t)) that covers almost all the length across the drift region during the turn-off since the collector-base junction is reversed biased.

### 2.5 IGBT Generation Improvement

Summarizes the main characteristics of five generations of IGBT chips. Each generation represents an incremental improvement in performance obtained through continuous process

optimization and new chip structures. To understand this evolution it is useful to consider each generation of the IGBT chip in terms of its surface structure and vertical design. The following sections present a brief description of the key technologies developed to allow dramatic improvements in chip efficiency.

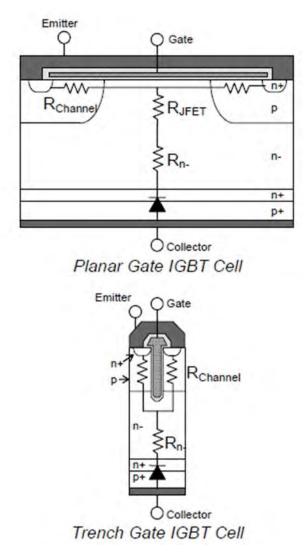

#### 2.5.1 Surface Structure

Early improvements in IGBT performance were attained primarily through finer surface patterns and shallow diffusion processing technologies. These techniques enabled significant reductions in cell size thereby allowing more active channel width per unit of chip area. The increased channel width reduces the RDS(on) of the MOSFET portion of the chip which yields reduced V<sub>CE</sub>(sat). The effect of this process refinement is highlighted by the simultaneous reduction of V<sub>CE</sub>(sat) and required chip area for the generation 1 through 3 IGBTs shown in Table 2.5.11. Unfortunately, this approach reached the point of severely diminishing returns due to the so-called "parasitic JFET" resistance between adjacent cells in the MOSFET portion of the device.

| Table 1 IGBT Generation Comparison 100A, 1200V IGBT   |                     |                     |                                 |                                 |                                 |  |

|-------------------------------------------------------|---------------------|---------------------|---------------------------------|---------------------------------|---------------------------------|--|

|                                                       | 1st<br>Gen.<br>1988 | 2nd<br>Gen.<br>1990 | 3 <sup>rd</sup><br>Gen.<br>1992 | 4 <sup>th</sup><br>Gen.<br>1998 | 5 <sup>tn</sup><br>Gen.<br>2000 |  |

| Family Name                                           | *******             | E-Series            | H-Series                        | F-Series                        | NF-Series                       |  |

| Base Wafer<br>Material                                | Epitaxial           | Epitaxial           | Epitaxial                       | Epitaxial                       | Float<br>Zone                   |  |

| Surface<br>Pattern                                    | 5μm<br>Planar       | 5μm<br>Planar       | 3μm<br>Planar                   | 1μm<br>Trench                   | 1μm<br>Trench<br>PCM            |  |

| Vertical<br>Design                                    | PT                  | PT                  | PT                              | PT                              | LPT-<br>CSTBT                   |  |

| V <sub>CE(sat)</sub> @<br>I <sub>C(rated)</sub>       | 3.5V                | 2.8V                | 2.5V                            | 1.9V                            | 1.9V                            |  |

| SWSOA                                                 | Over<br>300A        | Over<br>300A        | Over<br>300A                    | Over<br>400A                    | Over<br>400A                    |  |

| Chip Size                                             | 2p<br>12x12         | 2p<br>12x12         | 2p<br>10x10                     | 1p<br>9.1 x 11.5                | 1р                              |  |

| Gate Charge<br>Q <sub>G</sub>                         | 760nC               | 1100nC              | 500nC                           | 1100nC                          | 675nC                           |  |

| Short-Circuit<br>Current                              | 800A                | 800A                | 600A                            | 1500A<br>(Without<br>RTC)       | 500A                            |  |

| Short-Circuit<br>Withstanding<br>t <sub>W(crit)</sub> | 15μs                | 15μs                | 20μs                            | 5μs<br>20μs<br>With RTC         | 20μs                            |  |

Table 2.5.1 IGBT generation comparison

Figure 2.5.1 Unit cell comparison

One way to circumvent this problem is to adopt a high cell density trench-gate surface structure. A comparison of this structure to a conventional planar gate structure is illustrated in figure 2.5.1. In the trench gate structure the gate oxide and conductive polysilicon are formed in a deep narrow trench in the surface of the IGBT chip. This structure eliminates the parasitic JFET resistance and allows further reduction of cell size compared to conventional planar gated devices. The high density trench structure exhibits significant improvements in chip performance compared to planar gated predecessors. The significant advantage of the trench gate in terms of reduced  $V_{CE}(sat)$  can be seen in the transition from third to fourth generation in table 2.5.1. The

high cell density trench gate structure has two notable drawbacks. First, high cell density trench gate devices tend to have high short-circuit saturation currents. This characteristic degrades short-circuit withstanding capability of the device under low impedance fault conditions. To recover the short-circuit withstanding capability required for many industrial applications; it was necessary to add an additional current limiting circuit. An example of such a circuit is shown in figure 2.5.1 This circuit called an "RTC" or Real Time Control effectively restores short circuit withstanding capability by actively reducing the gate voltage when the current through the device exceeds approximately three times the device's nominal rated current. Unfortunately, the addition of the RTC to the module increases its complexity and cost. Secondly, the high cell density trench gate device often exhibits significantly increased gate capacitance compared to their planar-gated predecessors. This characteristic can also be seen in the transition from 3rd to 4<sup>th</sup> generation in table 2.5.1. The larger gate capacitance results in an undesirable increase in gate drive power requirements.

Figure 2.5.2 Effect of wide cell pitch on short circuit saturation current

One effective way to reduce the short-circuit saturation current, improve short-circuit ruggedness and reduce gate capacitance is to reduce the total channel width of the MOSFET part of the

IGBT structure. This can be accomplished by utilizing a wider trench pitch. Figure 2.5.2 shows the reduction of short circuit current resulting from increasing the trench pitch. This technique was found to be extremely useful for optimizing the trade-off between short circuit durability and VCE(sat). To allow easy adjustment of cell pitch using only two mask changes a technique called "PCM" or Plugged Cell Merged was developed. In the PCM device some portion on the trenches are "plugged" by shorting their polysilicon gate to the emitter electrode. The PCM structure is shown along with conventional planar and high cell density trench gate devices in figure 2.5.3. Another advantage to the PCM process is that it produces a distributed drain source capacitance in the MOSFET portion of the device. The distributed capacitance helps to damp oscillations during severe dynamic conditions. Unfortunately, reducing the channel width increases the RDS(ON) of the MOSFET portion of the device resulting in an increased VCE(sat). In the next section of this paper it will be shown that this undesirable increase in vertical structure.

Figure 2.5.3 IGBT surface structure comparison

#### 2.5.2 Vertical Structure

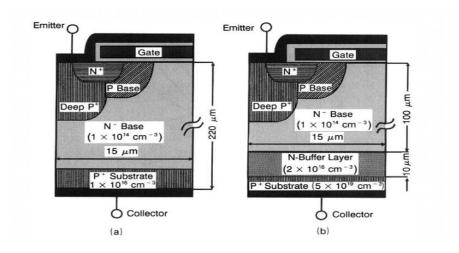

A schematic comparison of common IGBT vertical structures is shown in figure 2.5.4. The first successful industrial IGBT modules used almost exclusively the PT(Epi) (Punch-Through Epitaxial) structure. In this structure the main blocking junction is formed by the lightly doped n-depletion layer and relatively heavily doped n+ buffer layer. These layers are produced in epitaxial silicon. The main advantage of this structure is the ability to accurately control the resistivity and thickness of the n- layer to optimize the loss versus ruggedness trade-off. As a result devices using this structure often have the lowest losses on a per unit silicon area basis.

Figure 2.5.4 IGBT vertical Structure comparison

Unfortunately, there are two significant disadvantages of this structure. First, epitaxial silicon wafer material has a relatively high cost compared to the FZ (Float-Zone) wafer material that can be used with other structures. This is especially true for high voltage devices that require thicker epitaxial layers. Secondly, the long lifetime of carriers in the heavily doped n+ buffer layer must be modified to reduce turn-off losses. Typically this is done by electron irradiation or in some cases proton beam irradiation. This additional processing step adds cost and increases device to device characteristic variability. Another common vertical structure using less expensive FZ

wafer material is the conventional NPT (Non-Punch-Through) structure. The NPT device has an n- depletion layer with resistivity and thickness adjusted to block rated voltage. The lack of a buffer layer necessitates the use of a relatively thick high resistivity n- layer. The thick n- tends to provide good switching and short circuit ruggedness but higher V<sub>CE</sub>(sat). In order to reduce V<sub>CE</sub>(sat) it is necessary to make the n- layer thinner. This can be accomplished by thinning the silicon wafers. Special processing techniques have been developed to allow processing of optimally thin wafers. Unfortunately, as the n- thickness is optimized considering the blocking voltage versus V<sub>CE</sub>(sat) trade-off of the device the lack of a buffer layer gives rise to excessive leakage current at elevated temperatures.

Figure 2.5.5 Transition of technologies applied to IGBT chips (1200volts)

## **Chapter 3**

# Literature Review analysis

### 3.1 Equation's Overview

### 3.1.1 Poisson's Equation

It relates variations in electrostatic potential to space charge densities

$$div(\varepsilon \nabla \psi) = -\rho$$

Where:

- $\triangleright$   $\psi$  is the electrostatic potential

- $\triangleright$   $\varepsilon$  is the local permittivity

- $\triangleright \rho$  is the local space charge density

The local space charge density is the sum of contributions from all mobile and fixed charges, including electrons, holes, and ionized impurities.

The electric field is obtained from the gradient of the potential:

$$E = -\nabla \psi$$

## 3.1.2 Carrier Continuity Equation

The continuity equations for electrons and holes are defined by:

$$\begin{split} \frac{\partial n}{\partial t} &= \frac{1}{q} \frac{\partial J_n(x)}{\partial x} - R_n + G_L \\ \frac{\partial p}{\partial t} &= -\frac{1}{q} \frac{\partial J_p(x)}{\partial x} - R_p + G_L \end{split}$$

where,

- > n and p are the electron and hole concentration

- > J<sub>N</sub> and J<sub>P</sub> are the electron and hole current densities

- > G<sub>N</sub> and G<sub>p</sub> are the generation rates for electrons and holes

- $ightharpoonup R_n$  and  $R_P$  are the recombination rates for electrons and holes

- > q is the magnitude of electron charge.

It is sufficient in some cases solving only one carrier continuity equation.

#### 3.2 Allen R. Hefner Model

### 3.2.1 Expression for Transient Voltage & Stored Charge Decay

In Hefner transient modeling approach, the general ambipolar transport electron current expression

$$I_n(W(t)) = \frac{I_T(t)}{1 + \frac{1}{h}} + qAD\frac{\partial n(x,t)}{\partial x}$$

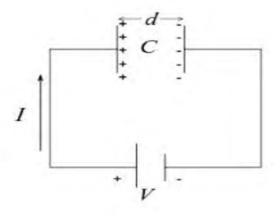

which was used to find an expression for the voltage rise (dV(t)/dt).  $I_n(W(t))=I_{MOS}$  as shown in Fig. 2.4.1 and it is important since it controls the operation of IGBT. Since the reverse bias does not increase rapidly and the depletion capacitance is partially charged in a short period of time,  $I_{MOS}$  current is instantaneous. An expression for  $I_{MOS}$  can be obtained if we consider the collection-base junction depletion capacitance as in Fig. 3.2.1

For the voltage V(t) between the plates, the charge per unit area  $q = \frac{\varepsilon_{Si}V(t)}{d}$ , where d is the distance between the plates and the rate of q change is

$$\frac{dq}{dt} = I(current)$$

Figure 3.2.1 the collector base depletion capacitance formation

As we know  $q(t) = C_{bcj}(t)V(t)$ , so

$$\frac{dq}{dt} = \frac{d}{dt} \left[ C_{bcj}(t)V(t) \right]$$

$$= V(t)\frac{dC_{bcj}(t)}{dt} + C_{bcj}(t)\frac{dV(t)}{dt}$$

and in terms of the junction capacitance of the reverse biased junction, the displacement current  $I_n(W(t))$  is

$$I_n(W) = V(t)\frac{dC_{bcj}(t)}{dt} + C_{bcj}(t)\frac{dV(t)}{dt}$$

(3.1)

The first term on the right hand side of the equation (3.1) was ignored by Hefner. The rate of change of  $C_{bcj}(t)$  should be included in calculating the displacement current since the capacitance varies with time as the depletion width changes with voltage. From equation (2.6) and the fact that J = I/A, where A is the device active area

$$I_n(W(t)) = \frac{I_T(t)}{1 + \frac{1}{b}} + qAD\frac{\partial p(x,t)}{\partial x}$$

And from Hefner's approach,

$$I_n(W(t)) = C_{bcj}(t) \frac{dV(t)}{dt} = \frac{I_T(t)}{1 + \frac{1}{b}} + \frac{2qAD_p}{1 + \frac{1}{b}} \frac{\partial p(x,t)}{\partial x}_{x=W(t)}$$

$$\Rightarrow \left(1 + \frac{1}{b}\right) C_{bcj}(t) \frac{dV(t)}{dt} = I_T(t) + 2qAD_p \frac{\partial p(x,t)}{\partial x}_{x=W(t)}$$

(3.2)

Hefner used equation (3.2) to obtain V(t) for the transient operation of IGBT. He implemented the concept of moving the redistribution current. In his transient approach, he neither used the steady state expression for p(x) nor did he linearize the steady state expression for p(x). Moreover he assumed  $C_{bcj}(t)$  to be constant with time, which is not so in reality.

His p(x) expression consists of two parts

$$p(x) = P_0 \left[ 1 - \frac{x}{W(t)} \right] - \frac{P_0}{W(t)D} \left[ \frac{x^2}{2} - \frac{W(t)x}{6} - \frac{x^3}{3W(t)} \right] \frac{dW(t)}{dt}$$

(3.3)

From equation (2.6) & (3.3)

$$I_n(W(t)) = \frac{bI_T(t)}{1+b} + qAD\frac{\partial p(x)}{\partial x}\Big|_{x=W(t)}$$

$$\Rightarrow I_n(W(t)) = \frac{I_T(t)}{1+\frac{1}{b}} + \frac{2qAD_p}{1+\frac{1}{b}}\frac{\partial p(x)}{\partial x}\Big|_{x=W(t)}$$

(3.4)

and instead of equation (3.1), Hefner applied  $I_n(W(t)) = C_{bcj}(t) \frac{dV(t)}{dt}$  in his approach. Integrating equation (3.3) in the base and multiplying by qA, the total charge Q

$$Q = qA \int_{0}^{W} p(x)dx$$

$$= qA \left[ x - \frac{x^{2}}{2W(t)} \right] - \frac{P_{0}}{W(t)D} \left[ \frac{x^{3}}{6} - \frac{W(t)x^{2}}{12} - \frac{x^{4}}{12W(t)} \right] \frac{dW(t)}{dt} \int_{0}^{W(t)} dt dt = qA \left[ P_{0} \left( W(t) - \frac{W(t)}{2} \right) \right] - \frac{P_{0}}{W(t)D} \left[ \frac{W(t)^{3}}{6} - \frac{W(t)^{3}}{12} - \frac{W(t)^{3}}{12} \right] \frac{dW(t)}{dt} = \frac{qAP_{0}W(t)}{2} - \frac{qAP_{0}}{WD} \times 0$$

$$Q = \frac{qAP_{0}W(t)}{2}$$

(3.5)

as can be seen  $\frac{dW(t)}{dt}$  has no effect on Q calculation.

We can find  $\frac{\partial p(x)}{\partial x}_{x=W(t)}$  from equation (3.3) as

$$\frac{\partial p(x)}{\partial x}_{x=W(t)} = \frac{P_0}{W(t)} - \frac{P_0}{W(t)D} \left[ \frac{2x}{2} - \frac{W(t)}{6} - \frac{3x^2}{3W(t)} \right] \frac{dW(t)}{dt}_{x=W(t)}$$

$$\frac{\partial p(x)}{\partial x} = \frac{-P_0}{W(t)} - \frac{P_0}{W(t)D} \left[ W(t) - \frac{W(t)}{6} - W(t) \right] \frac{dW(t)}{dt}$$

$$\frac{\partial p(x)}{\partial x} = \frac{-P_0}{W(t)} - \frac{P_0}{6D} \frac{dW(t)}{dt}$$

The hole current is  $-qA\frac{\partial p(x)}{\partial x}$  and from the above equation

$$\begin{split} -qAD\frac{\partial p(x)}{\partial x} &= \frac{qAP_0D}{W} - \frac{qAP_0D}{6D}\frac{dW(t)}{dt} \\ &= \frac{qAP_0D}{W(t)} - \frac{qAP_0}{6}\frac{dW(t)}{dt} \end{split}$$

$$AsQ = \frac{qAP_0W(t)}{2}$$

, So

$$-qAD\frac{\partial p(x)}{\partial x} = \frac{2QD}{W^2(t)} - \frac{Q}{3W(t)}\frac{dW(t)}{dt}$$

(3.6)

The first term on the right hand side of equation (3.6) is categorized by Hefner as the charge control component and the second term is categorized as the moving boundary redistribution component of the hole current.

From equations (3.4) & (3.6)

$$I_n(W(t)) = C \frac{dV(t)}{dt} = \frac{I_T(t)}{1 + \frac{1}{h}} - \frac{4QD_p}{1 + \frac{1}{h})W^2(t)} + \frac{Q}{3W(t)}\frac{dW(t)}{dt}$$

This equation can be expressed in a different way if  $-qA\frac{\partial p(x)}{\partial x}$  in equation (3.6) is modified as

$$-qAD\frac{\partial p(x)}{\partial x} = \frac{-2qAD_p}{1+\frac{1}{b}}\frac{\partial p(x)}{\partial x} = \frac{2QD}{W^2(t)} - \frac{Q}{3W(t)}\frac{dW(t)}{dt}$$

$$\Rightarrow -2qAD_p\frac{\partial p(x)}{\partial x} = \frac{2QD}{W^2(t)}\left(1+\frac{1}{b}\right) - \frac{Q}{3W(t)}\left(1+\frac{1}{b}\right)\frac{dW(t)}{dt}$$

$$\Rightarrow -2qAD_p\frac{\partial p(x)}{\partial x} = \frac{4D_pD_nQ}{W^2(t)(D_p+D_n)}\left(1+\frac{1}{b}\right) - \frac{Q}{3W(t)}\left(1+\frac{1}{b}\right)\frac{dW(t)}{dt}$$

$$\Rightarrow -2qAD_p\frac{\partial p(x)}{\partial x} = \frac{4D_pQ}{W^2(t)} - \frac{Q}{3W(t)}\left(1+\frac{1}{b}\right)\frac{dW(t)}{dt}$$

$$\Rightarrow -2qAD_p\frac{\partial p(x)}{\partial x} = \frac{4D_pQ}{W^2(t)} - \frac{Q}{3W(t)}\left(1+\frac{1}{b}\right)\frac{dW(t)}{dt}$$

(3.7)

From equation (3.4), we have

$$I_n(W(t)) = C \frac{dV(t)}{dt} = \frac{I_T(t)}{1 + \frac{1}{b}} + \frac{2qAD_p}{1 + \frac{1}{b}} \frac{\partial p(x, t)}{\partial x}_{x=W(t)}$$

That can be rearranged as

$$\left(1 + \frac{1}{b}\right)C(t)\frac{dV(t)}{dt} = I_T(t) + 2qAD_p\frac{\partial p(x,t)}{\partial x}_{x=W(t)}$$

Now using equation (3.7), and the fact that  $C(t) = C_{bcj}(t) = \frac{A\varepsilon_{Si}}{W_{bcj}(t)} = A\sqrt{\frac{2\varepsilon_{Si}N_B}{2V(t)}}$  and  $\frac{dW(t)}{dt} = \frac{-C}{qAN_B}\frac{dV(t)}{dt}$

the above equation yields

$$\left(1 + \frac{1}{b}\right) C_{bcj}(t) \frac{dV(t)}{dt} = I_T(t) - \frac{4D_p Q(t)}{W^2(t)} + \frac{Q(t)}{3W(t)} \left(1 + \frac{1}{ddb}\right) \frac{dW(t)}{dt}

\Rightarrow C_{bcj}(t) \frac{dV(t)}{dt} \left[1 + \frac{Q(t)}{3qAW(t)N_B}\right] = \frac{I_T(t) - \frac{4D_p Q(t)}{W^2(t)}}{1 + \frac{1}{b}}$$

$$\frac{dV(t)}{dt} = \frac{\left[I_T(t) - \frac{4D_pQ(t)}{W^2(t)}\right]}{C_{bcj}(t) \ 1 + \frac{1}{b}\left[1 + \frac{Q(t)}{3qAW(t)N_B}\right]}$$

(3.8)

where  $I_T(t)=I_T(0^-)$  for large inductive loads and  $I_T(t)=\frac{4D_pQ(t)}{W^2(t)}$  for the constant anode voltage in which  $\frac{dV(t)}{dt}=0$  indicating that the voltage and W(t) are constants. Equation (3.8) is Hefner's transient  $\frac{dV(t)}{dt}$  model for IGBT and Q(t) is expressed

Figure 3.2.2 A comparison of the theoretical and measured 10A infinite inductive load switching voltage waveforms for devices with different base lifetimes

By solving the following non-linear Hefner differential equation

$$\frac{dQ(t)}{dt} = -\frac{Q(t)}{\tau_{HL}} - \frac{4Q^2(t)I_{sne}}{W^2(t)A^2q^2n_i^2}$$

(3.9)

where  $I_{sne}$  is emitter electron saturation current(A) and  $n_i$  is the intrinsic carrier concentration  $cm^{-3}$ .

In Hefner's approach, the negative of the collected hole current  $I_P(W(t))$  consists of a charged control current ( $I_{CC}$ ) and redistribution current ( $I_R$ ), which make this model more complex. The expression (3.9) is not simple and  $Q_0$  cannot be easily determined since there is no expression for  $P_0$  which can be substituted for in  $Q_0$  equation to evaluate  $Q_0$  for magnitude. Also, this model did not consider the rate of change of C(t) in the calculation of the displacement current  $I_N$  (W(t)).

### 3.2.2 Redistribution time and Charge Control Current

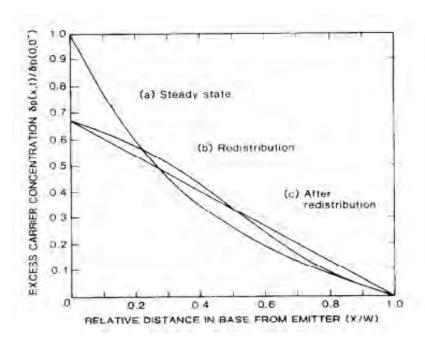

Representative excess carrier distribution in the wide-base bipolar transient at various moments during a constant anode voltage turn-off transient are shown in Fig. 3.2.3

Figure 3.2.3 The Excess carrier distribution in the base before (a), during (b), and after (c) the redistribution phase of a constant anode voltage switching transient, for W/L=2.5 and for  $I_n(x=0) << I_p(x=0)$ . The effect of the decay of the total excess carrier has been left out to illustrate the re distribution process.

When the base current is removed (constant anode voltage case) or the anode clamp voltage is reached (inductive load case), the carrier distribution in the base changes rapidly to one for which the total current at the emitter is equal to the hole current at the collector (from distribution (a) to (b) in Fig. 3.2.3), so that quasi-neutrality is maintained in the bipolar base. This reduction in the total device current is responsible for the initial rapid fall in current observed in the switching transient current waveform. The initial rapid fall consists principally of the steady-state net electron current at the collector (base current for the constant anode voltage case) and the component of holes drift current associated with the net electron current there. The remaining slowly decaying excess majority carrier store is responsible for the slowly decaying portion of the switching transient current wave form.

The boundary conditions on the electron and hole currents are different between the steady-state condition and the slowly decaying current phase. As a result, the electrons & holes that recombine can no longer be supplied be the divergence of their current densities as they are in steady-state, but are only supplied by (and thus reduce)the local excess carrier concentration. The curvature in the carrier distributions and the corresponding divergence of the current densities that remains after the initial rapid fall in emitter current acts to redistribute the excess carriers in the base from distribution (b) & (c) in Fig. 3.2.3. After the redistribution is complete, the excess carrier distribution and the terminal current are given in terms of the total excess carrier charge in the base, so the remainder of the waveform can be described using a charge control model.

The redistribution time and the relation between the charge and current after the redistribution is complete are found from the time-dependent ambipolar diffusion equation with  $I_n(W)=0$  and the total current equal to emitter edge of the base for negligible electron current at the injected into the emitter to the collector current gives:

$$\frac{\partial p(x,t)}{\partial t}_{x=0} = \frac{\partial p(x,t)}{\partial t}_{x=W}$$

(3.10)

The general solution to equation,

$$\frac{\partial^2 \delta p}{\partial x^2} = \frac{\delta p}{L^2} + \frac{1}{D} \frac{\partial \delta p}{\partial t}$$

with the conditions of

$$\delta p(x=0,t=0) \equiv P_{0,0}$$

(3.11)  $\delta p(W,t) = 0$  (3.12)

and equation (3.10) for W independent of time is

$$\delta p(x,t) = P_{0,0} \left( 1 - \frac{x}{W} \right) e^{\left( -\frac{t}{\tau_{HL}} \right)} + \sum_{m=1}^{\infty} A_m \sin(2m\pi x) e^{\left( -\frac{t}{\tau_m} \right)}$$

(3.13)

(3.14)

Where

$$\frac{1}{\tau_m} = \frac{1}{\tau_{HL}} + \frac{(2m\pi)^2 D_p}{W^2}$$

(3.15)

The first term of equation (3.13) is the linear charge control component of the distribution and the sine terms are the redistribution components which decay in time  $\tau_m$ . For the base width  $W_B = 93 \quad \Box \quad 10^{-6}m$  and other parameters,  $\tau_m = 0.1/m^2us$ . For times much larger than this, the redistribution terms become negligible and the current is determined by linear charge control component of the distribution.

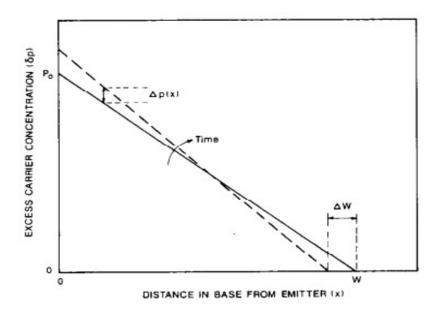

Figure 3.2.4 The carrier distribution in the base indicating the charge in excess carrier concentration with time due to the moving collector-base depletion edge boundary

The redistribution terms are independent of the total base charge and the integrated charge of the charge control term is equal to the total excess base charge:

$$Q(t) = \frac{qAP_{0,0}W}{2}e^{\left(-\frac{t}{\tau_{HL}}\right)}$$

(3.16)

Therefore, the current can only be described by a charge control model after the redistribution is complete. Using equations (3.13) & (3.15) for  $I_n(W) = 0$ , the charge control current is

$$I_T(t) = \frac{4D_p}{W^2}Q(t)$$

(3.17)

Because the integrated charge of each of the redistribution terms is zero, the value of current obtained by extrapolating the current decay waveforms back to the time of the initial rapid fall in current corresponds to the value of current obtained from equation (3.16) evaluated for the initial charge.

## Chapter 4

# **Simulations**

### 4.1 ATLAS A Physically-Based Simulator

In this thesis all the simulations involved are done with ATLAS from SILVACO which is a physically-based two and three dimensional device simulator. It predicts the electrical behavior of specified semiconductor structures and provides insight into the internal physical mechanisms associated with device operation.

Physically-based device simulators predict the electrical characteristics that are associated with specified physical structures and bias conditions. This is achieved by approximating the operation of a device onto a two or three dimensional grid, consisting of a number of grid points called nodes. By applying a set of differential equations, derived from Maxwell's laws, onto this grid it is possible to simulate the transport of carriers through a structure. This means that the electrical performance of a device can now be modeled in DC, AC or transient modes of operation.

The major advantages of Physically-based simulation are it is predictive, it provides insight, and it captures theoretical knowledge in a simplified version.

Physically-based simulation is different from empirical modeling. The objective of empirical modeling is to obtain analytic formulae that approximate existing data with good accuracy and minimum complexity. Empirical models provide efficient approximation and interpolation. They do not provide insight, or predictive capabilities, or encapsulation of theoretical knowledge. Physically-based simulation is an alternative to experiments as a source of data.

Physically-based simulation has become very important for two reasons. Firstly, it is almost always much quicker and cheaper than performing experiments. Secondly, it provides information that is difficult or sometime impossible to measure. The drawbacks of simulation are that all the relevant physics must be incorporated into a simulator and numerical procedures must be implemented to solve the associated equations. These tasks have been taken care of for users of ATLAS.

Users of physically-based device simulation tools must specify the problem to be simulated. Users of ATLAS specify device simulation problems by defining:

- 1. The physical structure to be simulated

- 2. The physical models to be used

- 3. The bias conditions for which electrical characteristics are to be simulated.

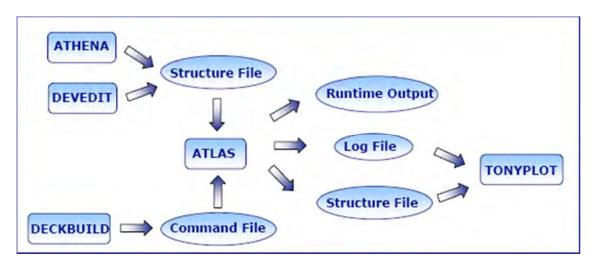

ATLAS here is used in conjunction with the VWF INTERACTIVE TOOLS. These include DECKBUILD, TONYPLOT, DEVEDIT, ATHENA and many more. DECKBUILD provides an interactive run-time environment. TONYPLOT supplies scientific visualization capabilities. DEVEDIT is an interactive tool for structure and mesh specification and refinement while ATHENA servers for semiconductor process simulation.

The interaction overview of SILVACO: ATLAS with other tools is shown in Fig. 4.1.1

Figure 4.1.1 Interaction with ATLAS software

We use the DECKBUILD command file input for the ATLAS environment to build our Trench IGBT and utilize all the outputs as well as TONYPLOT to conclude and visualize the simulated results.

Atlas input file contains a sequence of command lines and each line consists of a keyword or statement that identifies the command and a set of parameters.

In ATLAS there are four groups of statements that must occur in the correct order mentioned in Fig. 4.1.2

| Group                         | Statements |

|-------------------------------|------------|

|                               | MESH       |

| 1. Structure Specification    | ELECTRODE  |

| The second second             | CONTACT    |

| 2. Models specification       | MODELS     |

| 3. Numerical Method Selection | METHOD     |

|                               | LOG        |

| 4. Solution Specification     | SOLVE      |

|                               | LOAD       |

|                               | SAVE       |

Figure 4.1.2 Elements of ATLAS input deck in correct order

Each statement consists of a keyword that identifies the statement and a set of parameters. The general format is:

An example of a statement line is:

DOPING uniform n.type concentration=1.0e16 region=1 outfile=my.dop