# SMART AUTOMATION SYSTEM BASED ON FIELD PROGRAMMABLE GATE ARRAY

# A Thesis Submitted to the Dept. of Electrical & Electronic Engineering, BRAC UNIVERSITY in partial fulfillment of the requirements for the Bachelor of Science Degree in Electrical & Electronic Engineering

| FATIMA NAFSIA TASLIM | 12121050 |

|----------------------|----------|

| TASFIA LAMISA AHONA  | 12121053 |

| NISHAT TASNIM        | 12121056 |

| NAZIFA REZWANA HAQUE | 12121106 |

# **DECEMBER 2016**

# DECLARATION

We do hereby declare that the thesis work titled "Smart Automation System Based on Field Programmable Gate Array" is submitted to the Department of Electrical and Electronics Engineering of BRAC University in partial fulfillment of the requirement for the award of the degree of Bachelor of Science in Electrical and Electronics Engineering. The thesis work was carried out under the supervision of Dr. Md. Belal Hossain Bhuian. We declare that this project has not been presented elsewhere for assessment. Where material has been used from other sources it has been properly acknowledged/referred.

Date:

Signature of Supervisor

Dr. Md. Belal Hossain Bhuian

Thesis Supervisor

Signature of Authors

NazifaRezwanaHaque

ID-12121106

Fatima NafsiaTaslim

ID-12121050

TasfiaLamisaAhona

ID-12121053

NishatTasnim

ID-12121056

ii

# ACKNOWLEDGEMENT

We are extremely thankful to our supervisor Dr. Md. Belal Hossain Bhuian, Associate Professor, Department of Electrical and Electronic Engineering (EEE), BRAC University for his supervision and guidance. Without his continuous support this thesis would not have been possible. We would also like to thank every other individual without whose contribution the project would not be a success.

# ABSTRACT

Smart automation system is an evolution of human kind to a new era. These systems do all the jobs quickly and efficiently which saves time in our daily life, and in order to make these smart systems work more efficiently, faster and accurately we have used an FPGA Board (Field- Programmable Gate Array) in our thesis project. FPGA is an integrated circuit (IC) that allows programmer to create their own design in the field after manufacture and the core is able to operate different modules simultaneously. The main goal of our thesis is to implement four features that will save us from various accidents and wastage like home on fire or over flow of water and a little bit of smart security where we used PIR motion sensor, fire sensor and water sensor. In order to complete our desired project we had to work in three portions – compilation of module, synthesis and hardware implementation. FPGA board works digitally that lead us to converting all the sensor data or outputs to digital. We designed different modules for compiling different sensors on the FPGA board, then synthesis and hardware implementation were carried out accordingly. In spite of facing many challenges up to the hardware implementation we were successfully able to reach our desired goal.

# **Table of Contents**

| Acknowledgement                                             | iii     |

|-------------------------------------------------------------|---------|

| Abstract                                                    | iv      |

| Chapter 1: Introduction                                     | 6       |

| <b>1.1:</b> History of automation system                    | 6       |

| <b>1.2:</b> Today's automation system and its constraints   | 6-7     |

| 1.3: Our system with FPGA                                   | 7       |

| 1.4: Motivation                                             | 7       |

| <b>1.5:</b> Aim of the thesis                               | 8       |

| Chapter 2: Modeling concept of Verilog HDL in FPGA          | 9       |

| <b>2.1</b> : Introduction of HDL                            | 9       |

| <b>2.1.1:</b> A brief history of HDL                        | 9-10    |

| <b>2.1.2:</b> Different types of HDL                        | 10      |

| 2.2: Abridged History of Verilog HDL                        | 11      |

| <b>2.2.1:</b> Modern concept of Verilog HDL                 | 11-13   |

| <b>2.2.2:</b> Fundamental purposes for choosing Verilog HDL | 13      |

| <b>2.3:</b> An overview of FPGA                             | 13-14   |

| <b>2.3.1:</b> Reasons for working with FPGA                 | 14-15   |

| Chapter 3: Description of instruments we used               | 16      |

| 3.1: FPGA development board                                 | 16      |

| <b>3.1.1:</b> Types of FPGA devices                         | 16      |

| 3.1.2: ALTERA Cyclone-iii EP3C5E 144C8N development b       | oard-17 |

| 3.1.3: Pin configuration of ALTERA Cyclone-iii board | 17-20 |

|------------------------------------------------------|-------|

| <b>3.1.4:</b> Features                               | 20    |

| <b>3.2:</b> USB blaster                              | 21-22 |

| <b>3.2.1:</b> Features                               | 22    |

| 3.3: Sensors of our system                           | 22    |

| <b>3.3.1:</b> Grove flame sensor                     | 22-24 |

| <b>3.3.2:</b> PIR motion sensor                      | 24-25 |

| <b>3.3.3:</b> XINDA water sensor                     | 26-27 |

| Chapter 4: Implementation of the system              | 28    |

| <b>4.1:</b> Working procedure of sensors             | 28    |

| <b>4.1.1:</b> Flame sensor                           | 28    |

| <b>4.1.2:</b> Water sensor                           | 28    |

| <b>4.1.2.1</b> : Comparator                          | 28-29 |

| <b>4.1.3:</b> PIR motion sensor                      | 29    |

| <b>4.1.3.1:</b> Motion module                        | 30    |

| <b>4.1.3.2:</b> Counter module                       | 30    |

| 4.1.3.3: Control light module                        | 30    |

| <b>4.1.3.4:</b> Relay                                | 30    |

| <b>4.1.3.5:</b> Comparator                           | 31    |

| <b>4.2:</b> Demo door lock                           | 31    |

| <b>4.3:</b> Combined parallel compilation            | 31    |

| <b>4.3.1:</b> Pin assignment                         | 33    |

| Chapter 5: Result                                    | 34    |

| 5.1: Compilation Report                              | 34-37 |

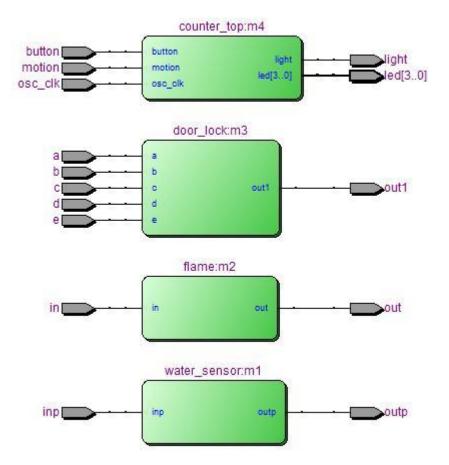

| <b>5.2:</b> RTL view                   | 38    |

|----------------------------------------|-------|

| Chapter 6: Challenges and future scope | 39    |

| <b>6.1:</b> Challenges                 | 39    |

| 6.2: Future Scope For Advancement      | 39    |

| Chapter 7: Conclusion                  | 40    |

| References                             | 41-42 |

| Appendix                               | 43-49 |

# List of figures

- 2.1 Types of HDL

- 3.1 ALTERA EP3C5E 144C8N Development Board

- **3.2** Core EP3C5

- 3.3 Combined FPGA Board

- 3.4 Block Diagram of the USB download cable

- 3.5 USB Blaster

- 3.6 Grove Flame Sensor

- 3.7 Top and Bottom View of Grove Flame Sensor

- 3.8 PIR Motion Sensor

- 3.9 Pin Specification of PIR Motion Sensor

- 3.10 XINDA Water Sensor

- 4.1 Working Procedure of Flame Sensor

- 4.2 Working Procedure of Water Sensor

- 4.3 Working Procedure of PIR Motion Sensor

- 4.4 Block diagram of Counter Module

- **4.5** Set up of the whole system

- 4.6 Pin Assignment of Total System

- **5.1** Compilation Report of Flame Sensor

- **5.2** Compilation Report of Water Sensor

- 5.3 Compilation Report of Motion Sensor

- **5.4** Compilation Report of Door Lock

- 5.5 Parallel Compilation Report

- 5.6 RTL View

# List of table

3.1 Types of FPGA devices

3.2 Specifications of Grove Flame Sensor

# **CHAPTER-1**

#### **INTRODUCTION**

#### **1.1: History of Automation System**

Home automation began with labor-saving machines such as washing machines and vacuum cleaners. These instruments do all the jobs quickly and efficiently which saves time in our daily life. Self-sufficient electric or gas powered home utilizations became sustainable in the 1900s with the introduction of electric power distribution and led to the launching of washing machines (1904), water heaters (1889), refrigerators, sewing machines, dishwashers, and dryers. In 1975, the first all-purpose home automation network technology, was developed, it is a communication protocol for electronic devices. Soon after that came the wall switch module. Smart systems, began to increase in popularity in the early 2000s, different technologies began to develop. Smart systems very quickly and swiftly started to become a more reasonable option, and therefore a more feasible technology for consumers. Domestic technologies, Office security home networking, and other gadgets began to emerge more in the market and their availability increased. By 2012, in the United States, according to ABI Research, 1.5 million home automation systems were installed According to Li et. al. (2016) there are three generations of home automation:

- 1. Wireless technology with proxy server, e.g. Zigbee automation;

- 2. Artificial intelligence controls electrical devices, e.g. amazon echo;

- 3. Robot buddy "who" interacts with humans, e.g. Robot Rovio, Roomba.

#### 1.2: Today's automation systems and its constraints

Nowadays smart homes and offices are mainly about security and protection. Our smart systems are viable, and they help to make sure that our homes and offices aren't consuming unnecessary energy. These systems also helps to alert us against dangerous hazards like fire and even signals us against intruders even though we are home or not. Even when we are far away we will still be connected to our homes, and when the house is occupied, the high level of automation enables more convenience, control and safety from any part of your property. All these advance features helped us to reduce our worries and increased our

level of enjoyment. Current developments in home automation include remote mobile control, automated lights, automated thermostat adjustment, scheduling appliances, mobile/email/text notifications etc. Some of the constraints of the home automation system with Arduino and other microcontroller are the speed is less, does not work in parallel and its difficult to introduce it in the market.

#### 1.3: Our system with FPGA

In our smart system we have implemented an FPGA Board, by using this board our system will work faster, efficiently and accurately than the other home automation systems. Our system consumes less power compared to the other home automation systems by operating all the features used simultaneously.

# **1.4: Motivation**

Our motive was to create a smart sensing system that can work more efficiently and effectively as we are using more sophisticated board. There were several things which encouraged us to do the project with FPGA rather than other microcontrollers are:

- FPGA are not stuck to any hardware configuration, but the microcontrollers are stuck to the configuration that the supplier provides, they cannot be rewired.

- FPGA's code is executed in parallel and microcontroller is executed sequentially.

- FPGA is faster in more complex solutions and work more efficiently and accurately.

- FPGA has incredible flexibility on its price and lower power consumption.

- It has a vast range of capability and can be interfaced through different ports.

- It is easier to build desired system and design it on chip.

There are some reasons to choose this project;

- To make an easier hardware implementation for experiment

- Easy as a basic stage of abstraction and synthesis

- There are parallel operations with the sensors

#### 1.5: AIM of the Thesis

The purpose of this thesis work is to introduce a smart system using the FPGA Board. In this research we have designed a smart sensing system using FPGA, which will keep the people safe from various accidents which can take place in their home or even offices where they spend most of their time. Another aim of our thesis work is to reduce power consumption. Through our work we will try to reduce power wastage, which is a major problem nowadays in our society. Every person loves their home, thus to protect their home and keep it safe everyone should take a few initiatives like protect the house from fire or water overflow etc. In our project we have included such features through which a person can easily detect whether their house caught an unwanted fire or if there is water flow from their water tank or washroom especially bathtub or bucket. Most people often tend to forget to turn off the lights or fan of the room, so through our smart system we have even included a feature of automatic turning the lights and fan off of the room by using a motion sensor.

# **CHAPTER-2**

# Modeling concept of Verilog HDL in FPGA

#### 2.1: Introduction of HDL

A Hardware Description Language (HDL) is a particular code used to portray the structure and conduct of electronic circuits, and most generally, the digital logic circuits. In electronics a HDL is a language from computer language used for formal description of electronic circuits. HDL is used to describe any digital circuits in the form of architectural, gate level and behavior of discrete electronic system. It is a very easy language which can describe circuit operation, its design and tests to verify its operation at any level of circuits and it is found to be an excellent programming language for FPGAs and CPLDs. The Top-down design and hierarchical design method allows the design time; design cost and design errors to be reduced. Another major advantage is related to complex designs, which can be managed and verified easily. HDL provides the timing information and allows the design to be described in gate level and register transfer level. Reusability of resources is one of the other advantages.

The three common HDLs are Verilog, VHDL, and SystemC. Of these, SystemC is the newest. The HDLs will allow fast design and better verification. Nowadays, Verilog and VHDL are very common in industries. Verilog, one of the main Hardware Description Language standardized as IEEE 1364 is used for designing all types of circuits. It consists of modules and the language allows Behavioral, Dataflow and Structural Description of any complex circuit.

#### 2.1.1: A brief History of HDL

Hardware description languages were first appeared in the late 1960s, looking like more traditional languages. The first that had a lasting effect was described in 1971 in C. Gordon Bell and Allen Newell's text Computer Structures and that text presented the idea

of register transfer level. At first it is used in the ISP language to define the behavior of the Digital Equipment Corporation (DEC) PDP-8.

Later, the language became more common with the introduction of DEC's PDP-16 RT-Level Modules (RTMs) and a book telling their use. At least two implementations of the basic ISP language (ISPL and ISPS) followed. ISPS was well suitable to define the relations between the inputs and the outputs of the design and was quickly adopted by commercial teams at DEC, as well as by a number of research teams.

# 2.1.2: Different Types of HDL

The most common language used in widespread are Verilog HDL and VHDL.

Figure-2.1: Types of HDL

There are different HDLs available for describing analog circuits, digital circuits and PCBs. HDLs for digital circuit design other than Verilog and VHDL are as follows.

- VHDL (VHSIC HDL)

- Verilog

- TL-Verilog (Transaction-Level Verilog)

- THDL++ (Template HDL inspired by C++)

- SystemVerilog

- SystemTCL

- SystemC

#### 2.2: Abridged History of Verilog HDL

The history of Verilog HDL goes back to the 1980s, a company called Gateway Design Automation developed a logic simulator, Verilog-XL, and with it a hardware description language. It was created by PrabhuGoel and Phil Moorby between 1983 and 1984. Cadence Design Systems acquired Gateway in 1989, and with it the rights to the language and the simulator. Cadence now has full proprietary rights to Gateway's Verilog and the Verilog-XL, the HDL-simulator that would become the de facto standard for the next decade [3]. Originally, Verilog was only intended to describe and allow simulation, the automated synthesis of subdivisions of the language to physically realizable structures and gates and was developed after the language had achieved widespread usage. In 1990, Cadence put only the language into the public domain, with the intention that it should become a standard, non-proprietary language. Later, the Verilog HDL maintained as a nonprofit making group. In December 1995 Verilog HDL became IEEE Std. 1364-1995.

Verilog is a combination of the words "verification" and "logic". So after that there was a further revision in 2005. Moreover, Accellera have also developed a new standard, System Verilog, which extends Verilog. Then the System Verilog became an IEEE standard (1800-2005) in 2005.

#### 2.2.1 Modern concepts of Verilog HDL

A design methodology is very important to understand before working with the Verilog language because the designer must use the best design methodology to do efficient Verilog HDL based on the designs. There are basically two types of digital design methodologies: a top- down design methodology and a bottom- up design methodology.

#### In a top-bottom methodology:

The desired design-style of all designers is the top-down one. A real top-down design allows primary testing, easy modification of different technologies, structured system design and offers many other benefits. But it is very tough to follow a pure top-down design. Due to this fact most designs are a combination of both methods, employing some key elements of both design styles.

#### In a bottom –up methodology:

The old-fashioned method of electronic design is bottom-up. Each design is performed at the gate-level using the standard gates. With the increasing complexity of new designs this approach is nearly impossible to maintain. New systems consist of ASIC or microprocessors with a complexity of thousands of transistors. These traditional bottom-up designs have to give way to new structural, hierarchical design methods. Without these new perform it would be impossible to handle the new complexity. Verilog supports designing at many different levels of abstraction. Three of them are very important: Verilog is both a behavioral and structural language. There are four level of abstraction to describe a module which can be changed without any change in the settings.

They are as follows:

Behavioral or algorithmic level Dataflow level Gate level Switch level

#### **Behavioral or algorithmic level:**

This level defines a system by simultaneous algorithms (Behavioral). Each algorithm itself is sequential, that means it consists of a set of instructions that are executed one after the other. Functions, Tasks and Always blocks are the main elements. There is no regard to the structural comprehension of the design.

#### **Dataflow level:**

For small circuits, the gate level modeling method works very well because the number of gates is inadequate and designer can instantiate and links every gate individually. However in complex design the number of gates is very large. Thus executing the function at a level higher than gate level is good idea. Dataflow modeling has become a popular design approach as logic synthesis tools have become sophisticated. This approach permits the designer to concentrate on optimizing the circuit in terms of data flow.

#### Gate level

Within the logic level the features of a system are defined by logical links and their timing properties. All signals are discrete signals. They can only have definite logical values (`0', `1', `X', `Z`) [3]. The usable operations are predefined logic primitives (AND, OR, NOT etc gates). Using gate level modeling might not be a good idea for any level of logic design. Gate level code is generated by tools like synthesis tools and these lists are used for gate level simulation and for backend.

#### Switch level

In Verilog this is the lowest level of abstraction. A module can be implemented in different forms like as switch, nodes and the interlinked between them. Design for this level requires knowledge of switch level implementation.

#### 2.2.2: Fundamental purposes for choosing Verilog HDL

It is easy to learn and easy to use, due to its similarity in syntax to the C programming language.

In the same design different abstraction level can be mixed.

There is availability of Verilog HDL libraries for post-logic synthesis simulation.

Most of the synthesis tools support Verilog HDL. This makes the language of selection for most of the designers.

The Programming Language Interface (PLI) is a powerful feature that allows the user to write custom C code to interact with the internal data structures of Verilog.

Designers can modify a Verilog HDL simulator to their needs with the PLI.

#### 2.3: An Overview of FPGA

FPGA (Field- Programmable Gate Array) is an integrated circuit (IC) that allow programmer to create their own design or program in the field after manufacture. Basically we can consider an FPGA as a blank state that means designer can create their very own configure file or bit file. The bit file loaded on FPGA will act like the digital circuit the designer designed. There is no processor in FPGA to run the software until the designer build one, it is up to the designer to create a simple file like an and gate to multi-core processor . A Hardware Description Language (HDL) is required for FPGA configuration. The elementary building block of a FPGA is programmable logic block (PLB) or configurable logic block (CLB). This logic block can similarly be assigned the function to act as computer memory which permits to store certain values and also between this logic blocks there are reconfigurable wiring circuitry. The logic block of a FPGA consist of a 4 input LUT (Look up Table), a programmable multiplexer which assists to choose whether the FPGA be programmed in registered or non-registered output and finally a flip-flop for storage. FPGA is a volatile device, they store their configure file in a RAM so after losing the power they forget about the configure file. Designers have control over the hardware with FPGA.

#### 2.3.1: Reasons for working with FPGA

- Massively parallel data processing: The ability of parallel processing is

one of the huge advantages of FPGA. Since we have done our thesis on

smart sensing system so we needed to interface a lot of sensors in parallel.

Processors are usually more functional for routine control of particular

circuits and have fixed serial port but in FPGA blocks are allowed to

configure at any ports. There are enough spaces for choosing port.

Designer can choose any of the port according to their need. FPGA permits

to do hall bunches of processing at once and this is the main reason for

choosing FPGA for our thesis.

- **Super-fast:** FPGA is a super-fast device. Since the customer can determine the hardware structure of FPGAs so FPGA can be programmed to process larger data with few clock cycle, whereas this is not possible with the processor [20].Because data flow is limited by processor bus (16-bit, 32 bit, etc.) and the processing speed. A basic FPGA have input output blocks and serial functionality works in giga byte per second comparing to microcontrollers and other devices that works in 100 megahertz.

- Field programmable: As it is named field programmable so updates and feature development can be carried out even after delivery consumer's site. . It is feasible to define and utilize processor and user-specific hardware functions on only one chip by using FPGA. This solution gives engineers the chance to control the hardware because of its great flexibility. Designers can change and update whole design (FPGA on the processor and

other logic circuits) by only changing the code on FPGA, without any change on circuit board layout. Thus if designers face any problem in manufacturing there is a scope to modify it.

- It can do anything: It is possible with FPGA to do anything. Designers can build a microcontroller, DSP (Digital Signal Processor) or anything they want. FPGAs have no fixed hardware processor thus it is programmable according to designers desire and able to do anything in digital demand.

- Extremely short time to market: Through the use of FPGAs the development of hardware prototypes is drastically accelerated as a huge part of the hardware development process is shifted into ip core design, which can take place in parallel. In addition, because of the early availability of hardware prototypes, time-consuming activities like the start-up and debugging of the hardware are brought onward alongside to the overall development.

- **Performance gain for software applications:** Complex designs are often handled through software implementations in arrangement with high-performance processors. In this case FPGAs offers a spirited alternative, which by means of parallelization and customization for the definite task even establishes a supplementary performance gain

- **Real time applications:** FPGAs are absolutely suitable for applications in time-critical systems. On the contrary to software based solutions with real time operating systems, FPGAs provide real deterministic performance. By means of the featured flexibility even complex computations can be accomplished in enormously short periods.

- **Cost Effective:** In this board we can use all sensors simultaneously and this board has huge number of I/O ports. Thus, by using only this one board we can perform a lot of tasks side by side and at a minimum cost.

# **CHAPTER-3**

# **Description of Instruments We Used**

# 3.1: FPGA Development Board

# 3.1.1: Types of FPGA Devices

| Device Family                            | Voltage required                                               |  |  |

|------------------------------------------|----------------------------------------------------------------|--|--|

| FPGA                                     |                                                                |  |  |

| Stratix V, Stratix IV and Stratix III    | As specified by VCCGM or VCCPD                                 |  |  |

| Stratix II, Stratix II GX and Stratix GX | As specified by VCCEL                                          |  |  |

| Arria 10                                 | As specified by VCCPGM or VCCIO                                |  |  |

| Arria V                                  | As specified by VCCPD                                          |  |  |

| Arria II GX                              | As specified by V <sub>CCPD</sub> OR V <sub>CCIO</sub> Of BANK |  |  |

| Arria GX                                 | As specified by VCCEL                                          |  |  |

| Cyclone V                                | As specified by VCCPGM or VCCPD                                |  |  |

| Cyclone IV                               | As specified by VCCA OR VCCIO                                  |  |  |

| Cyclone III                              | As specified by VCCA OR VCCIO                                  |  |  |

| Max 10                                   | As specified by VCCIO                                          |  |  |

| Configuration                            |                                                                |  |  |

| EPCS                                     | 3.3v                                                           |  |  |

| EPCQ                                     | 3.3v                                                           |  |  |

| EPCQ-L                                   | 1.8v                                                           |  |  |

|                                          | 1                                                              |  |  |

Table-3.1 Types Of FPGA Devices

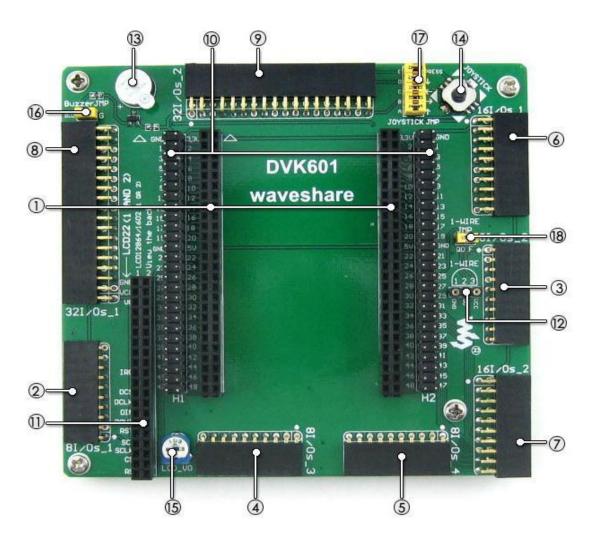

### 3.1.2: ALTERA Cyclone-iii EP3C5E 144C8N Development Board

We have chosen EP3C5-C board for our thesis.

Figure-3.1 ALTERA Cyclone-iii EP3C5E 144C8N Development Board

# 3.1.3: Pin Configuration of ALTERA Cyclone-iii Board

- 1. FPGA CPLD core board connector: for easily connecting core boards which integrate an FPGA CPLD chip onboard

- 2. 8I/Os\_1 interface, for connecting accessory boards/modules

- 3. 8I/Os\_2 interface, for connecting accessory boards/modules

- 4. 8I/Os\_3 interface, for connecting accessory boards/modules

- 5. 8I/Os\_4 interface, for connecting accessory boards/modules

- 6. 16I/Os\_1 interface, for connecting accessory boards/modules

- 7. 16I/Os\_2 interface, for connecting accessory boards/modules

- 8. 32I/Os\_1 interface, for connecting accessory boards/modules

- 9. 32I/Os\_2 interface, for connecting accessory boards/modules

All the I/O interfaces above:

- Capable of being simulated as USART, I2C, SPI, PS/2, etc.

- Capable of driving devices such as FRAM, FLASH, USB, Ethernet, etc.

- 10. FPGA expansion connectors

- o FPGA pins are accessible on expansion connectors

- $\circ~$  for connecting SDRAM accessory board

- 11. LCD interface, for connecting LCD22, LCD12864, LCD1602

- ONE-WIRE interface: easily connects to ONE-WIRE devices (TO-92 package), such as temperature sensor (DS18B20), electronic registration number (DS2401), etc.

- 13. Buzzer

- 14. Joystick: five positions

- 15. Potentiometer: for LCD22 backlight adjustment, or LCD12864, LCD1602 contrast adjustment

- 16. Buzzer jumper

- 17. Joystick jumper

- 18. ONE-WIRE jumper

For jumpers 16-18:

- short the jumper to connect to I/Os used in example code

- open the jumper to connect to other custom pins via jumper wires

Core EP3C5:

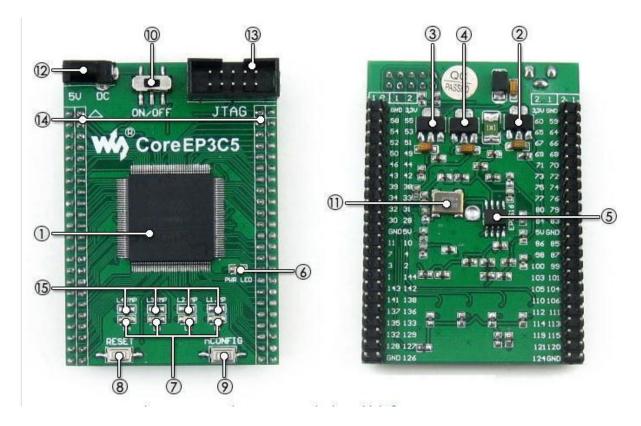

Figure-3.2 Core EP3C5

1. EP3C5E144C8N: the ALTERA Cyclone III FPGA device which features:

• **Operating Frequency:** 50MHz

- **Operating Voltage:** 1.15V∼3.465V

- Package: QFP144

- **I/Os:** 82

- $\circ~$  Les: 5K

- **RAM:** 414kb

- $\circ~$  PLLs: 2

- Debugging/Programming: supports JTAG

- 2. AMS1117-3.3, 3.3V voltage regulator

- 3. AMS1117-2.5, 2.5V voltage regulator

- 4. AMS1117-1.2, 1.2V voltage regulator

- 5. EPCS16, onboard serial FLASH memory, for storing code

- 6. Power indicator

- 7. LEDs

- 8. Reset button

- 9. Nconfig button: for re-configuring the FPGA chip, the equivalent of power resetting

- 10. Power switch

- 11. 50M active crystal oscillator

- 12. 5V DC jack

- 13. JTAG interface: for debugging/programming

- 14. FPGA pins expander, VCC, GND and all the I/O ports are accessible on expansion connectors for further expansion

- 15. LED jumpers, short the jumpers to drive the LEDs [19].

# 3.1.4: Features

- 1. Minimum power consumption

- 2. Design security feature

- 3. Increased system integration [20].

Figure-3.3 Combined FPGA Board

# 3.2: USB Blaster

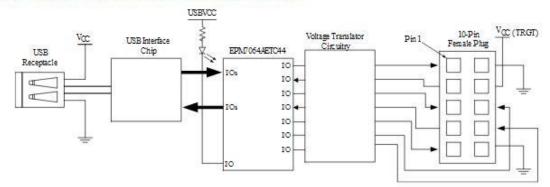

The USB blaster download cable interfaces a USB port on a host computer to an Altera FPGA mounted on a printed circuit board. The cable sends arrangement information from the PC to a standard 10-stick header associated with the FPGA. We can utilize the USB Blaster cable to iteratively download configuration information to a system in prototyping or to program data into the system during construction.

# Block Diagram of the USB Download Cable

Figure-3.4 Block Diagram of the USB Download Cable

# Figure 3.5 USB Blaster

# 3.2.1: Features

- 1. High speed

- 2. Stable

- 3. Internal FT245R+CPLD designed

- 4. Supports 1.2-5V programming voltage

- 5. Supports Signal Tap II embedded logic analyzer

- 6. Supports Nios II of embedded processor communication and debugging [17].

# 3.3: Sensors of Our System:

# 3.3.1: Grove Flame Sensor

The Grove - Flame Sensor can be applied to identify fire source or other light sources of the wavelength in the range of 760nm - 1100 nm. It depends on the YG1006 sensor which is a fast and high sensitive NPN silicon phototransistor. Because of its black epoxy, the sensor is sensitive to infrared radiation.

Figure-3.6 Grove Flame Sensor

# Working Mechanism:

A fire sensor identifies the nearness of flame or flares, in extremely dangerous situations, flame sensors work to minimize the dangerous connected with flame. There are a few distinct categories of flame sensors, some will raise an alarm while others may initiate a fire concealment framework or deactivate an ignitable fuel line. In our project we used The Grove- Flame sensor, to mainly detect the fire dangers in houses, offices and even hotels. The grove flame sensor is connected to the Field Programmable Gate Array (FPGA) Board, following the correct pin assignments. After all the pin assignments are done correctly and the simulation is 100% completed the sensor is ready for work. Now whenever the sensor detects any kind of flame in the vicinity, it gives an output of 1 and if it does not detect any flame then it gives out an output of 0.

Figure-3.7 Top and Bottom View of Grove Flame Sensor

Grove flame sensor has the following features like:

- Grove Interface

- High Photo Sensitivity

- Rapid Response Time

- Easy to use

- Sensitivity is adjustable

# **Specifications:**

| Item                       | Min  | Typical | Max  | Unit |

|----------------------------|------|---------|------|------|

| Voltage                    | 4.75 | 5.0     | 5.30 | VDC  |

| Current                    | /    | 20      | /    | mA   |

| Range ofSpectral Bandwidth | 760  | 940     | 1100 | nm   |

| Detection Range            | 0    | -       | 1    | m    |

| Response Time              |      | 15      |      | μS   |

| Operating Temperature      | -25  | -       | 85   | °C   |

Table-3.2 Specifications of Grove Flame Sensor

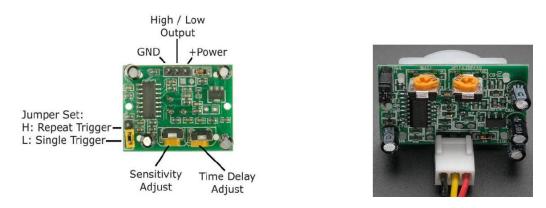

# 3.3.2: PIR Motion Sensor

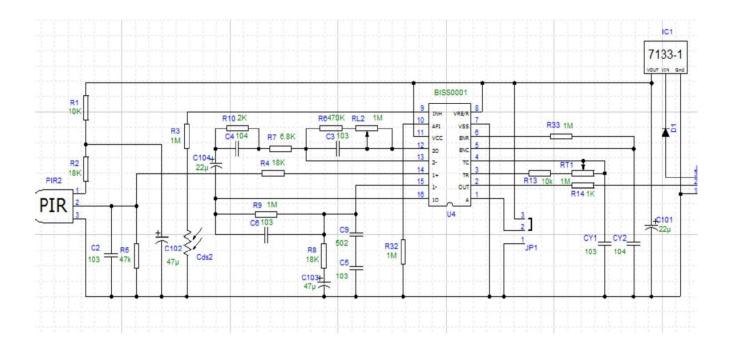

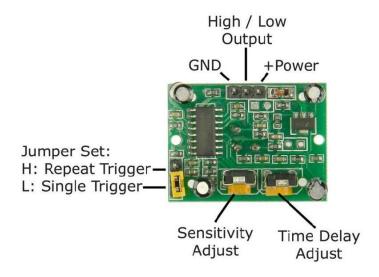

Figure-3.8 PIR Motion Sensor

PIR Motion sensors are most complex sensors than many of the other sensors, since there are multiple factors that affect the sensors input and output. There are two slots in the sensor, each slot is made of a special material that is sensitive to IR light.

When the sensor is inactive, both slots detect the same amount of IR, the ambient amount radiated from the room or walls of the room or outdoors. When a warm body like a human or animal passes by, it first stops one half of the PIR sensor, which gives a positive differential change between the two halves. When the warm body leaves the sensing area, the reverse happens, thus the sensor generates a negative differential change. These change pulses are what is detected. PIR sensors allows us to sense motion, it is used to detect whether a human has moved in or out of the sensors range.

PIR Sensors are small, economical, and easy to use and does not wear out. For these reasons they are commonly found in appliances and devices used in homes or businesses

areas. They are often referred to as PIR, "Passive Infrared", "Pyro electric", or "IR motion" sensor.

Figure-3.9 Pin Specification Of PIR Motion sensor

For our PIR Motion Sensor:

- i. Red cable is + voltage power,

- ii. Black cable is ground power

- iii. Yellow is the signal out.

# **Specifications:**

- Digital output: 3.3v (High representing binary 1 when gets motion and less representing 0 without motion)

- Working voltage: 5V-20V DC

- Delay: 0.3s 18s (adjustable)

- Trigger: H repeatable (default), L unrepeatable.

- Power Consumption: 65mA

- Delay time: Adjustable (.3->5min)

- Sensing range: less than 120 degree, within 7 meters

- Temperature:  $-15 \sim +70$

- Dimension: 32\*24 mm, distance between screw 28mm, M2, Lens dimension in diameter: 23mm

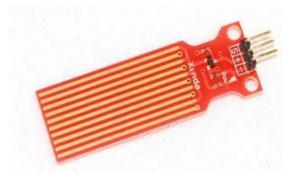

### 3.3.3: XINDA Water Sensor:

The Water Sensor indicates whether the sensor is waterless, wet or completely submerged in water by measuring the conductivity. In our project we have used this sensor to detect the level of water mainly in bathrooms, water tanks and for normal household purpose or for office usage, to keep a track if water is overflowing anywhere inside the building compound.

Figure-3.10 XINDA Water Sensor

#### **Features:**

- Grove compatible interface

- Low power intake

- 2.0cm x 2.0cm twig module

- High sensitivity

# **Applications:**

- Detecting Rainfall

- Liquid Leakage

- Tank Overflow Detector

# **Specifications:**

- Product name: water level sensor

- Working voltage: DC3-5 v

- Working current: less than 20 ma

- Sensor types: simulation

- Detection area: 40 mm x 16 mm

- Production process: FR4 double-sided tin

- Working temperature: 10 C-30 C

- Working humidity: 10% to 90% without condensation

- Product weight: 3.5 g

- Product size: 62 mm x 20 mm x 8 mm

# Pin definition:

- "S" stand for signal input

- "+" stand for power supply

- "-" stand for GND

# Chapter- 4

# **Implementation of the System**

#### 4.1: Working procedure of sensors

#### 4.1.1: Flame Sensor

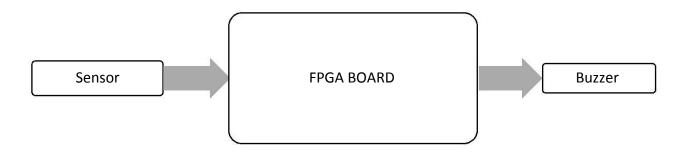

Our first project idea was to make an alarm system that is going to detect any kind of fire. We used the grove flame sensor which gives a high voltage at room temperature when flame is detected. We made a simple module to run an alarm in occurrence of any fire. In this module we used gate level synthesis to get the job done. We adjusted the threshold that can detect a flame from match stick. The FPGA output gets into a buzzer.

Figure-4.1 Working Procedure of Flame Sensor

#### 4.1.2: Water sensor

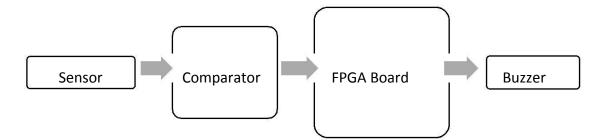

Our second project idea was to create a water overflow system. Water sensor gives the output voltage according to the water level and the voltage starts from around 2.7 volts and increases up to 3.7~3.8 due to certain pressure of water at room temperature. We set up a threshold voltage of 2.85 to detect water. We used gate level synthesis to do this sensor work.

#### 4.1.2.1: Comparator

As this sensor is analog in nature it was necessary to make the output digital. As FPGA doesn't take analog signal and cannot process we used a comparator circuit that led the output high when water is detected. Using an Im358 operational amplifier we made up a little comparator. We put the threshold voltage as the inverting output and the sensor

output as the non-inverting. When the sensor output crosses the threshold, it will send high signal or binary 1 to the board. The FPGA output gets into a buzzer.

Figure-4.2 Working Procedure of Water Sensor

#### 4.1.3: PIR motion sensor

Figure-4.3 Working Procedure of PIR Motion Sensor

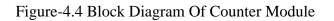

PIR motion sensor is sensitive to infrared light to detect any kind of motion. To configure this sensor to a simple module we made a behavioral level of abstraction so that it will give a output voltage corresponding to motion. Getting any motion causes 3.3 volts and no motion means 0 in room temperature. Our plan was then to add a sequential timing constraint to measure the period of motionless environment. It is to make an energy saving system that prevents unnecessary power consumption. To make this work we created a big module consisting of sub-modules that are instantiated within one schematic. There are 3 sub-modules under the mother module.

Detecting motion it will deliver respective output where motion gives a high voltage and otherwise 0 voltages to the counter module. Motion sensitivity was fixed at the midpoint so that it only covers a small room for experimental convenience.

# 4.1.3.2: Counter module

MOTION MODULE

COUNTER MODULE

CONTROL LIGHT MODULE

# 4.1.3.3: Control light module

# 4.1.3.4: Relay

Output from FPGA switches the relay and the relay operates light.

### 4.1.3.5: Comparator:

Though this sensor gives a high voltage as output, sometimes it flickers about some milivolts which occurs a fluctuating current. To solve any kind of disruption and to make the output smoother we used a comparator circuit where 3.1 is the threshold voltage. Whenever the sensor supplies a voltage greater than this it means some motion occurred and it's taken as binary 1.

#### 4.2: Demo door lock

We made a simple door lock system which takes a 5 bit binary input as a key and opens the door at the correct combination. In this system it is set to 10001.

### 4.3: Combined parallel compilation

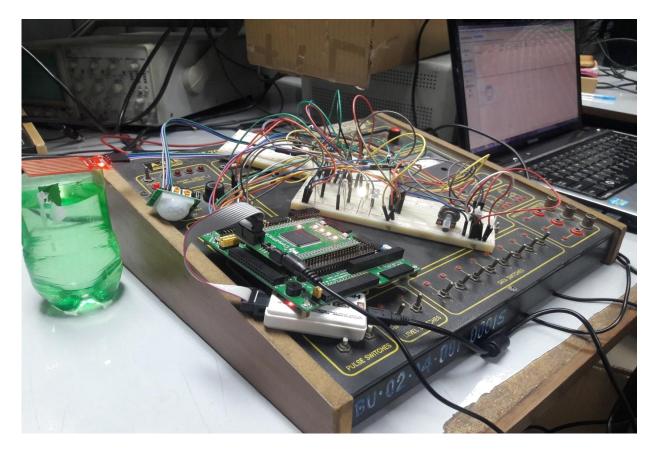

Our first and foremost goal was to operate multiple systems simultaneously in parallel at one time. FPGA gives us the privilege to make these ideas work together. To run them together we had to create a master module which enslaves these slave modules. Instantiating these modules we got them on one track those results in the three sensors sensing simultaneously and giving out the results with same efficiency, speed and accuracy. Adding the project files into one master project, using multiple i/o ports for hardware configuration and merging them into the master module was all we had to do.

Figure- 4.5 Set up of the Whole System

# 4.3.1: Pin assignments

| le | Ed     | lit View Processing                                           | Tools Window He                                                 | elp 💎                                                      |                                        |                                                                  |                                                                    |                                                                                              |                                          |

|----|--------|---------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------|

| G  | Groups |                                                               |                                                                 | ₽×                                                         | •0000000000000000000000000000000000000 |                                                                  |                                                                    |                                                                                              |                                          |

|    |        |                                                               |                                                                 |                                                            |                                        |                                                                  |                                                                    |                                                                                              |                                          |

| 5  |        | Node Name                                                     | Direction                                                       | Locati                                                     |                                        | Top View                                                         |                                                                    | Dod.                                                                                         |                                          |

| -  | ⊳      | led[30]                                                       | Output Group                                                    |                                                            | 8                                      | Wire Bond, with Expose                                           | d Pad                                                              | 0-                                                                                           |                                          |

| ]  |        | < <new group="">&gt;</new>                                    |                                                                 |                                                            | 0                                      | 10 M 10                                                          |                                                                    | 8                                                                                            |                                          |

|    |        | 36 - 130                                                      |                                                                 |                                                            | 8                                      |                                                                  |                                                                    | 8                                                                                            |                                          |

| 5  |        |                                                               |                                                                 |                                                            | ê                                      |                                                                  |                                                                    | 8                                                                                            |                                          |

| 2  |        |                                                               |                                                                 |                                                            | 20                                     |                                                                  |                                                                    | Do.                                                                                          |                                          |

|    |        |                                                               |                                                                 |                                                            |                                        | Cy clone III                                                     |                                                                    | 8-                                                                                           |                                          |

|    |        |                                                               |                                                                 |                                                            |                                        |                                                                  |                                                                    |                                                                                              |                                          |

|    |        |                                                               |                                                                 |                                                            |                                        | 192231219002                                                     |                                                                    | X ==                                                                                         |                                          |

| >  |        |                                                               |                                                                 |                                                            | -                                      | EP3C5E144C8                                                      |                                                                    |                                                                                              |                                          |

| >  |        |                                                               |                                                                 |                                                            |                                        | EP3C5E144C8                                                      |                                                                    |                                                                                              |                                          |

|    | 4      |                                                               |                                                                 | •                                                          |                                        | EP3C5E144C8                                                      |                                                                    | 0000                                                                                         |                                          |

| 4  | 1000   |                                                               | -                                                               | •                                                          |                                        |                                                                  |                                                                    | 00000                                                                                        |                                          |

|    | 1000   | Named: * 😽 😽                                                  | ≫Edit: X ✓                                                      | 1 2 20                                                     | -                                      |                                                                  |                                                                    | Filter: Pins: a                                                                              | 1                                        |

|    | ×      | Named: * 🕶 🕷<br>Node Name                                     | Direction                                                       | Location                                                   | I/O Bank                               | VREF Group                                                       | I/C                                                                | Filter: Pins: a                                                                              | 1                                        |

|    | ×      | Named: * 🗸 🕷<br>Node Name                                     | Direction                                                       | Location                                                   | I/O Bank                               | VREF Group<br>B4_N0                                              | I/C<br>2.5 V                                                       | Filter: Pins: a                                                                              | all<br>Rese                              |

|    | ×      | Named: *  Node Name                                           | Direction<br>Input<br>Input                                     | Location<br>PIN_58<br>PIN_55                               | I/O Bank<br>4<br>4                     | VREF Group<br>B4_N0<br>B4_N0                                     | I/C<br>2.5 V<br>2.5 V                                              | Filter: Pins: a<br>O Standard<br>(default)<br>(default)                                      | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. |

|    | ×      | Named: * •<br>Node Name                                       | Direction<br>Input<br>Input<br>Input<br>Input                   | Location<br>PIN_58<br>PIN_55<br>PIN_54                     | I/O Bank<br>4<br>4<br>4                | VREF Group<br>84_N0<br>84_N0<br>84_N0<br>84_N0                   | I/C<br>2.5 V<br>2.5 V<br>2.5 V                                     | Filter: Pins: a<br>O Standard<br>(default)<br>(default)<br>(default)                         | 1                                        |

|    | ×      | Named: * •<br>Node Name<br>a<br>b<br>b<br>button<br>c         | Direction Input Input Input Input Input Input Input Input Input | Location<br>PIN_58<br>PIN_55<br>PIN_54<br>PIN_53           | I/O Bank<br>4<br>4<br>4<br>3           | VREF Group<br>B4_N0<br>B4_N0<br>B4_N0<br>B3_N0                   | I/C<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V                   | Filter: Pins: 2<br>D Standard<br>(default)<br>(default)<br>(default)<br>(default)            | 1                                        |

|    | ×      | Named: * • (¥<br>Node Name<br>a<br>b<br>b<br>button<br>c<br>d | Direction Input Input Input Input Input Input Input Input Input | Location<br>PIN_58<br>PIN_55<br>PIN_54<br>PIN_53<br>PIN_52 | I/O Bank<br>4<br>4<br>4<br>3<br>3      | VREF Group<br>B4_N0<br>B4_N0<br>B4_N0<br>B3_N0<br>B3_N0<br>B3_N0 | I/C<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V          | Filter: Pins: a<br>Standard<br>(default)<br>(default)<br>(default)<br>(default)<br>(default) | 1                                        |

|    | 2<br>X | Named: * •<br>Node Name<br>a<br>b<br>b<br>button<br>c         | Direction Input Input Input Input Input Input Input Input Input | Location<br>PIN_58<br>PIN_55<br>PIN_54<br>PIN_53           | I/O Bank<br>4<br>4<br>4<br>3           | VREF Group<br>B4_N0<br>B4_N0<br>B4_N0<br>B3_N0                   | I/C<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V<br>2.5 V | Filter: Pins: 2<br>D Standard<br>(default)<br>(default)<br>(default)<br>(default)            | 1.000                                    |

Figure-4.6 Pin Assignment of Total System

### **CHAPTER-5**

#### Results

After merging the modules and hardware connection the system worked as it was meant to. Our experiment was successful. Here are the compilation reports.

#### **5.1:** Compilation reports

• Compilation of flame sensor:

| ile Edit View Project Assignments Processing Too                                                                                                                                                                                     | ls Window I                                              | Help 💎                                                                                          |                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 🗅 🚅 🖬 🎒 🎒 👗 🖻 🛍 🗠 🖓 📑 fame                                                                                                                                                                                                           |                                                          | - 🕱 🖞 🖉 🍕                                                                                       | 🔉 💿 🕨 🦻 🔭 🕲 😒                                                                                                             |

| oject Navigator 🗗 🗙                                                                                                                                                                                                                  | ٩                                                        | Compilation Report 🛛 🔀                                                                          |                                                                                                                           |

| Files                                                                                                                                                                                                                                | Table o 🗗                                                | Flow Summary                                                                                    |                                                                                                                           |

| → Files<br>abd flame.v<br>→ Hierarchy B Files a <sup>5</sup> Design Units                                                                                                                                                            | Flow<br>Flow<br>Flow<br>Flow<br>Flow                     | Flow Status<br>Quartus II Version<br>Revision Name<br>Top-level Entity Name<br>Family<br>Device | Successful - Sun Dec 11 13:33:04 2<br>11.0 Build 208 07/03/2011 SP 1 SJ \<br>flame<br>flame<br>Cyclone III<br>EP3C5E144C8 |

| isks 5 ×                                                                                                                                                                                                                             | Flow                                                     | Timing Models  Total logic elements                                                             | Final  0 / 5,136 (0 %)                                                                                                    |

| low: Compilation                                                                                                                                                                                                                     | <ul> <li>Analy</li> <li>Fitter</li> <li>Asser</li> </ul> | Total combinational functions<br>Dedicated logic registers<br>Total registers                   | 0 / 5,136 (0 %)<br>0 / 5,136 (0 %)<br>0                                                                                   |

| Task                                                                                                                                                                                                                                 | D 🗋 Time(                                                | Total pins                                                                                      | 2/95(2%)                                                                                                                  |

| ✓ Analysis & Synthesis                                                                                                                                                                                                               |                                                          | Total virtual pins<br>Total memory bits                                                         | 0                                                                                                                         |

| Edit Sattings                                                                                                                                                                                                                        |                                                          | EI II INTER ALT I                                                                               | 0 / 423,936 (0 %)                                                                                                         |

|                                                                                                                                                                                                                                      | < >>                                                     | ·                                                                                               |                                                                                                                           |

| Type Message<br>Warning: Some pins have incomple<br>Warning: Ignored filter at flame<br>Warning: Ignored create_clock at<br>Warning: No clocks defined in de<br>Warning: Parallel compilation is<br>Warning: Ignored filter at flame | e.sdc(1): (<br>flame.sdo<br>esign.<br>s not lice:        | osc_clk could not be matc<br>c(1): Argument <targets><br/>nsed and has been disable</targets>   | hed with a port or pin<br>is not an object ID                                                                             |

| System /\ Processing (107) /\ Extra Info /\ Info (93) /                                                                                                                                                                              | 21                                                       |                                                                                                 | ۲.                                                                                                                        |

|                                                                                                                                                                                                                                      | Warning (14)                                             |                                                                                                 | essed (6) / Flag                                                                                                          |

| Message: 0 of 16                                                                                                                                                                                                                     |                                                          |                                                                                                 | ▼ Locate                                                                                                                  |

|                                                                                                                                                                                                                                      |                                                          |                                                                                                 | 100% 00:00:14                                                                                                             |

Figure-5.1 Compilation Report of flame sensor

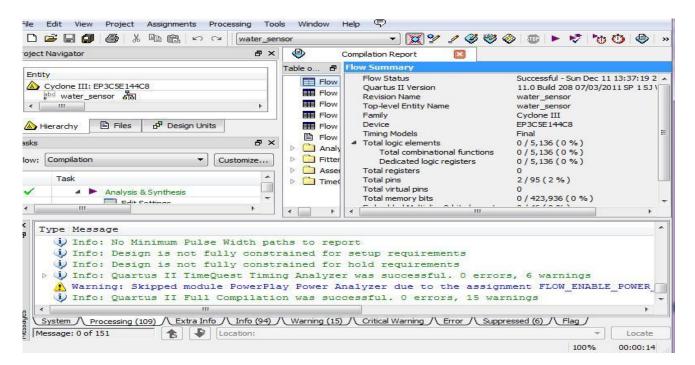

• Compilation of water sensor:

Figure-5.2 Compilation Report of Water sensor

• Compilation of motion sensor:

| oject Navigator 🛛 🗗 🗙                                                                                                                                                                                                                                                                                                     | •                                                             | Compilation Report 🛛 🗵                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                     |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Entity  Cyclone III: EP3C5E 144C8  Cyclone III: EP3C5E 144C8  Files Design Units  Ks  Hierarchy Files Design Units  Ks  Compilation Customize  Task  Analysis & Synthesis  III Customize  Task                                                                                                                            | Table o<br>Flow Flow Flow Flow Flow Flow Flow Flow            | Flow Summary Flow Status Quartus II Version Revision Name Top-level Entity Name Family Device Timing Models  Total logic elements Total combinational functions Dedicated logic registers Total pins Total virtual pins Total virtual pins Total memory bits | Successful - Sun Dec 11 13:40:29<br>11.0 Build 208 07/03/2011 SP 1 S<br>counter_top<br>Cyclone III<br>EP3CSE144C8<br>Final<br>37 / 5,136 ( < 1 % )<br>37 / 5,136 ( < 1 % )<br>32 / 5,136 ( < 1 % )<br>32 8 / 95 ( 8 % )<br>0<br>0 / 423,936 ( 0 % ) |    |

| Type Message<br>i Info: No Minimum Pulse Width pat<br>i Info: Design is not fully constr<br>i Info: Design is not fully constr<br>i Info: Quartus II TimeQuest Timin<br>Warning: Skipped module PowerPla<br>i Info: Quartus II Full Compilation<br>System Processing (132) (Extra Info / Info (108))<br>Message: 0 of 253 | ained for<br>ained for<br>g Analyze<br>y Power A<br>m was suc | setup requirements<br>hold requirements<br>r was successful. 0 error<br>nalyzer due to the assign<br>cessful. 0 errors, 32 war                                                                                                                               | nment FLOW_ENABLE_POWE                                                                                                                                                                                                                              | te |

Figure-5.3 Compilation Report of Motion sensor

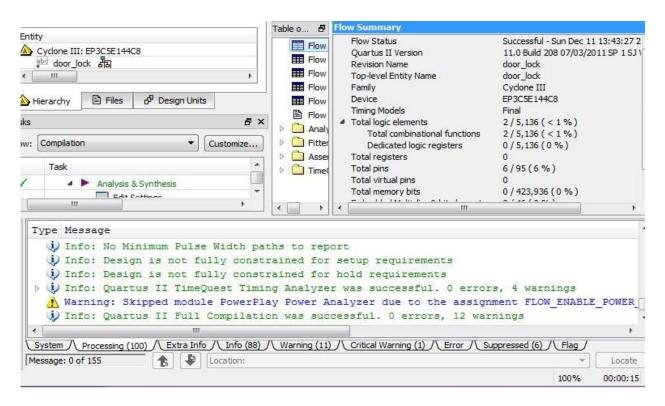

• Compilation of door lock:

Figure-5.4 Compilation Report of Door Lock

• Parallel compilation report:

| oject Navigator 🗗 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 🕸 final_p                                                                                                                                    | roject.v 🗵 🔮 Compilation Rep                                                                                                                                                                                                                                                                          | ort 🔀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|